1175 Bordeaux Drive, Sunnyvale, California 94089 Sales (408) 743-3355 Admin. (408) 743-3300 Cust. Service (408) 743-3325

MEMORY DATA

## **MEMORIES**

Prepared by Technical Information Center

Motorola has developed a very broad range of reliable memories for virtually any digital data processing system application. Complete specifications for the individual circuits are provided in the form of data sheets. In addition, a selector guide is included to simplify the task of choosing the best combination of circuits for optimum system architecture.

The information in this book has been carefully checked; no responsibility, however, is assumed for inaccuracies. Furthermore, this information does not convey to the purchaser of microelectronic devices any license under the patent rights of the manufacturer.

New Motorola memories are being introduced continually. For the latest releases, and additional technical information or pricing, contact your nearest authorized Motorola distributor or Motorola sales office.

MECL is a trademark of Motorola Inc.

## TABLE OF CONTENTS

|                           | Page          |

|---------------------------|---------------|

|                           |               |

| Alphanumeric Index        | v             |

| Tuphanamono maox          | v             |

| OLIA PTED 4               |               |

| CHAPTER 1                 |               |

| Memories Selector Guide   |               |

|                           |               |

| CHAPTER 2 — MOS Dynamic I | RAMs          |

| MCM4116B                  | 16K × 1       |

| MCM4517<br>MCM6665A       | 16K × 1       |

| MCM6665B                  | 64K × 1       |

| MCM6665C                  | 64K × 12-43   |

| MCM6256                   | 256K × 1      |

| MCM6257                   | 256K × 1      |

| CHAPTER 3 — MOS Static RA | Ms            |

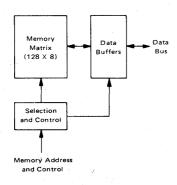

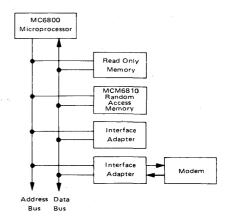

| MCM6810                   | 128 × 8       |

| MCM2114                   | 1K × 4        |

| MCM6147<br>MCM2016H       | 4K × 1        |

| MCM2167H                  | 16K × 1       |

| MCM6116                   | 2K × 8        |

| MCM6168H                  | 4K × 4        |

| MCM6169H<br>MCM6164H      | 4K × 4        |

|                           |               |

| CHAPTER 4 — MOS EPROMs    |               |

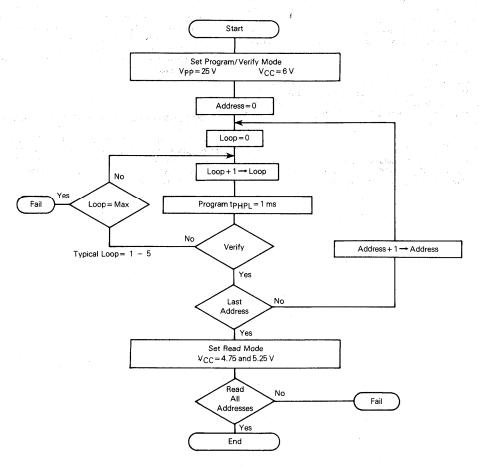

| MCM68764                  | 8K × 84-3     |

| MCM68766                  | 8K × 84-9     |

| CHAPTER 5 - MOS EEPROMS   |               |

| MCM2833                   | 4K × 85-3     |

| MCM2864                   | 8K × 85-11    |

| CHAPTER 6 - MOS ROMs      |               |

| MCM6670, 6674             | 128 × (7 × 5) |

| MCM66700, 710             | 128 × (7 × 9) |

| 66714, 720                |               |

| 66730, 734<br>66740, 750  |               |

| 66751, 760                |               |

| 66770, 780                |               |

| 66790<br>MCM65516         | 2K × 8        |

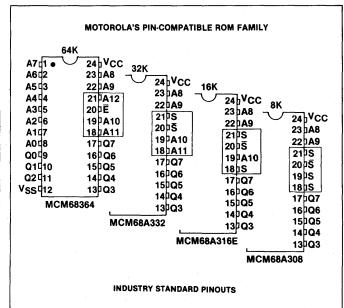

| MCM68A316E                | $2K \times 8$ |

| MCM68A332                 | 4K × 8        |

| MCM68364                  | 8K × 8        |

| MCM68365<br>MCM68366      | 8K × 8        |

| MCM68367                  | 8K × 8        |

| MCM68368                  | 8K × 86-57    |

| MCM68369<br>MCM68370      | 8K × 8        |

| MCM68370<br>MCM68380      | 8K × 8        |

| MCM63128                  | 16K × 86-77   |

| MCM63256                  | 32K × 86-83   |

| MCM65256                  | 32K × 8       |

## TABLE OF CONTENTS (Continued)

|                                                                                                                                            |                                                                                                                                                | Page                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

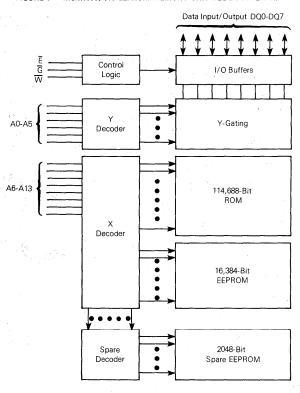

| CHAPTER 7 — Other MOS I<br>MCM68HC34<br>MCM6836E16<br>6836R16                                                                              | Memories  Dual-Port RAM Memory Unit  Combination ROM/EEPROM Memory Unit                                                                        |                                                    |

| CHAPTER 8 — TTL RAMs  MCM93415  MCM93422  93L422  MCM93425                                                                                 | 1K × 1                                                                                                                                         | 8-7                                                |

| CHAPTER 9 — TTL PROMS  MCM7621 7621A MCM7641 7641A MCM7643 7643A MCM7649 7649A MCM7681 7681A MCM7685 7685A MCM76161 76161A MCM76165 76165A | 512 × 4  512 × 8  1K × 4  512 × 8  1K × 8  2K × 4  2K × 8  4K × 4                                                                              | 9-79-119-159-199-23                                |

| CHAPTER 10 — MECL RAM MCM10143 MC10H145 MCM10145 MCM10144 MCM10152 MCM10415 MCM10422 MCM10470 MCM10474                                     | 8 × 2<br>16 × 4<br>16 × 4<br>256 × 1<br>256 × 1<br>1K × 1<br>256 × 4<br>4K × 1<br>1K × 4                                                       | 10-70<br>10-10<br>10-14<br>10-18<br>10-25<br>10-25 |

| CHAPTER 11 — MECL PROMCM10147<br>MCM10139<br>MCM10146<br>MCM10149                                                                          | Ms  128 × 1  32 × 8  1024 × 1  256 × 4                                                                                                         | 11-7<br>11-12                                      |

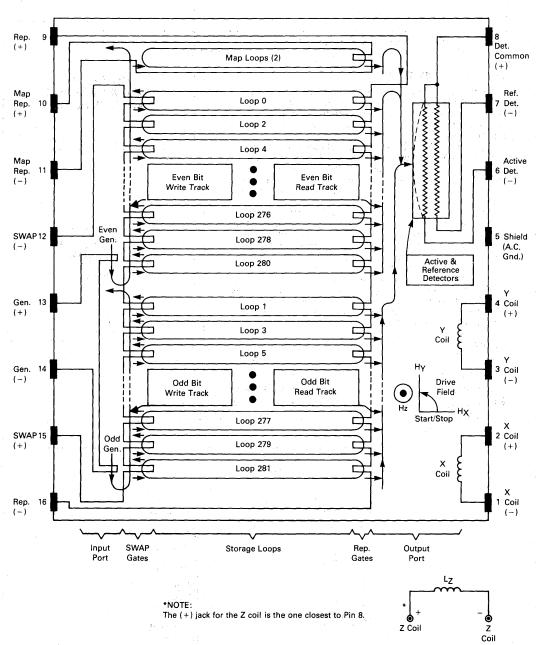

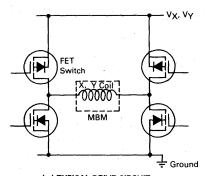

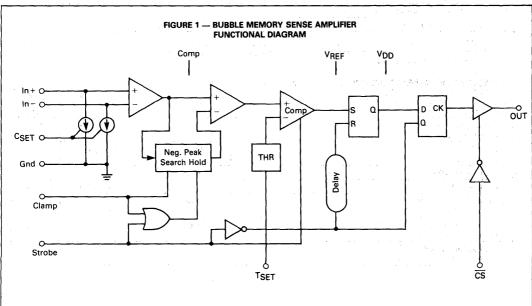

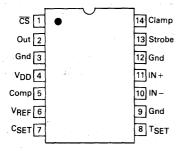

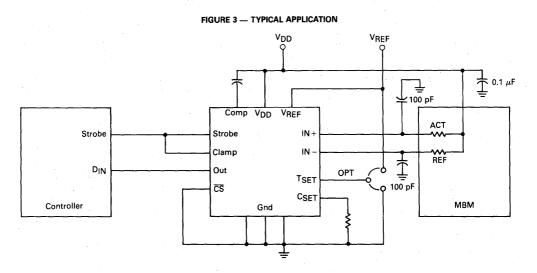

| MBM2256<br>MBM2011A<br>MC34044<br>MC34046S<br>34047S<br>SC42468<br>SC42584<br>42585                                                        | 256K × 1  1M × 1  Bubble Memory Sense Amplifier Single Bubble Memory Operations Driver  Bubble Memory Coil Predriver Bubble Memory Controllers | 12-13<br>12-23<br>12-27<br>12-32<br>12-37          |

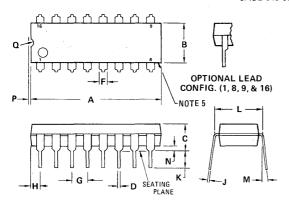

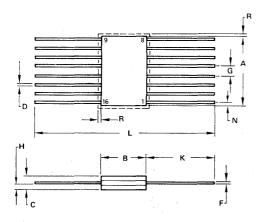

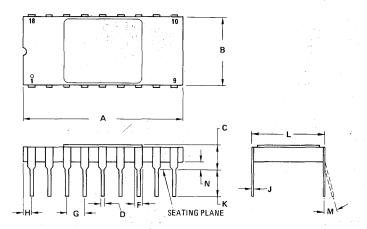

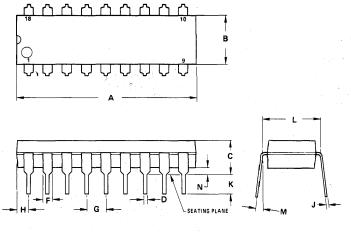

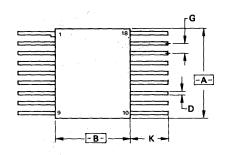

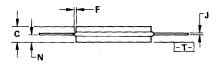

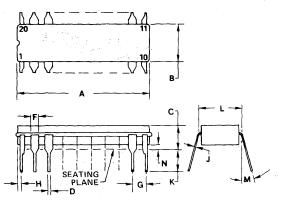

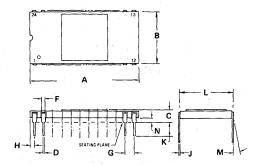

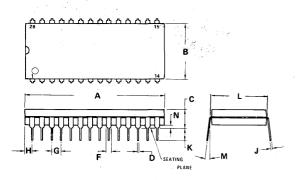

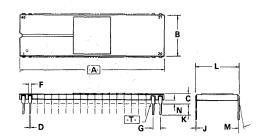

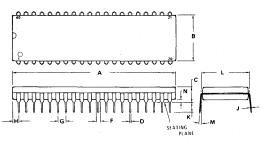

| CHAPTER IS — Mechanical                                                                                                                    | Data                                                                                                                                           | 13-1                                               |

## ALPHANUMERIC INDEX

| Device Pag   | ge Device Page  |

|--------------|-----------------|

| MBM2011A     | I3 MCM66746-3   |

| MBM225612-   |                 |

| MC10H145     | -7 MCM66750     |

| MC34044      |                 |

| MC34046S     |                 |

| MC34047S     |                 |

| MCM1013911-  |                 |

| MCM10143     |                 |

| MCM1014410-1 |                 |

| MCM1014510-1 |                 |

| MCM10146     |                 |

| MCM1014711-  |                 |

| MCM10149     |                 |

| MCM10152     |                 |

| MCM10415     |                 |

| MCM10422     |                 |

| MCM10470     |                 |

| MCM10474     |                 |

| MCM2016H     |                 |

| MCM2114      |                 |

| MCM2167H     |                 |

| MCM2833      |                 |

| MCM2864      |                 |

| MCM4116B     |                 |

| MCM4517      |                 |

| MCM61L16     |                 |

| MCM61L47     | 14 MCM76161A    |

| MCM6116      | 33 MCM76165     |

| MCM6147      | 14 MCM76165A    |

| MCM6164H     | 41 MCM76219-3   |

| MCM6168H     |                 |

| MCM6169H     | 40 MCM7641 9-7  |

| MCM62562-4   |                 |

| MCM62572-4   |                 |

| MCM63128     | 77 MCM7643A     |

| MCM63256     |                 |

| MCM65256     |                 |

| MCM65516     | 24 MCM76819-19  |

| MCM6665A     | 17 MCM7681A     |

| MCM6665B     |                 |

| MCM6665C     |                 |

| MCM66706-    | -3 MCM93L4228-7 |

| MCM667006-1  |                 |

| MCM667106-1  | 10 MCM934228-7  |

| MCM66714     | 10 MCM934258-12 |

| MCM667206-1  | 10 SC4246812-32 |

| MCM667306-1  | 10 SC42584      |

| MCM66734     | 10 SC4258512-37 |

## **MOTOROLA MEMORIES**

Motorola has developed a very broad range of reliable MOS and bipolar memories for virtually any digital data processing system application.

New Motorola memories are being introduced continually. This selector guide lists all those available as of May 1984. For later releases, additional technical information or pricing, contact your nearest authorized Motorola distributor or Motorola sales office.

Data sheets may be obtained from your in-plant VSMF Data Center, distributors, Motorola sales office or by writing to:

Literature Distribution Center Motorola Semiconductor Products Inc. P.O. Box 20912 Phoenix, AZ 85036

### Notes:

Operating temperature ranges:

MOS - 0°C to 70°C

ECL - 0°C to 75°C

TTL - Military -55°C to + 125°C, Commercial 0°C to 75°C

\*To be introduced.

(Not all speed selections shown)

1300 mil package

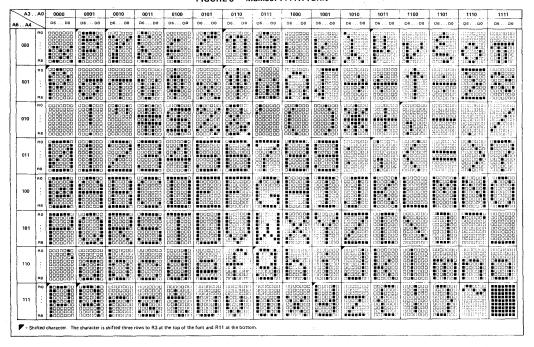

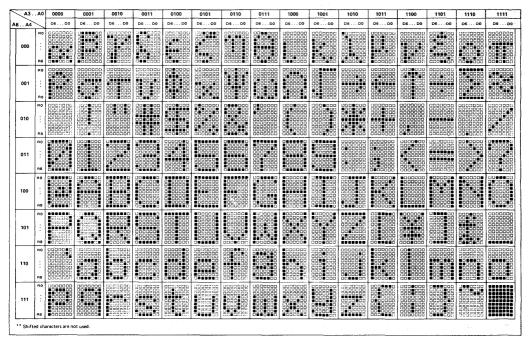

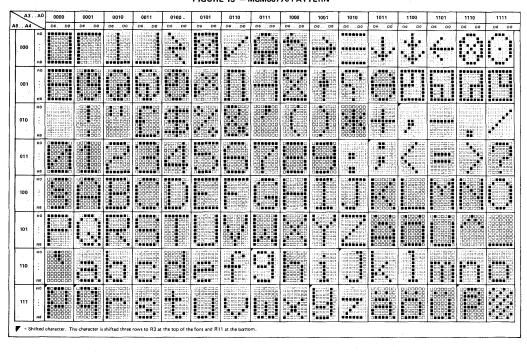

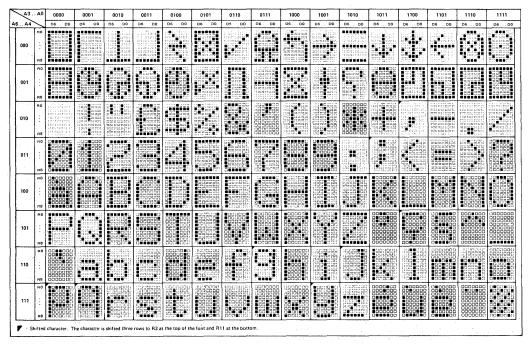

2Character generators include shifted and unshifted characters, ASCII alphanumeric control, math, Japanese, British, German, European and French symbols.

<sup>3</sup>Standard Patterns for MOS ROMs:

MCM68A316EP91 — Universal Code Coverter and Character Generator

Generator

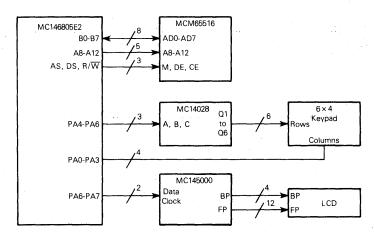

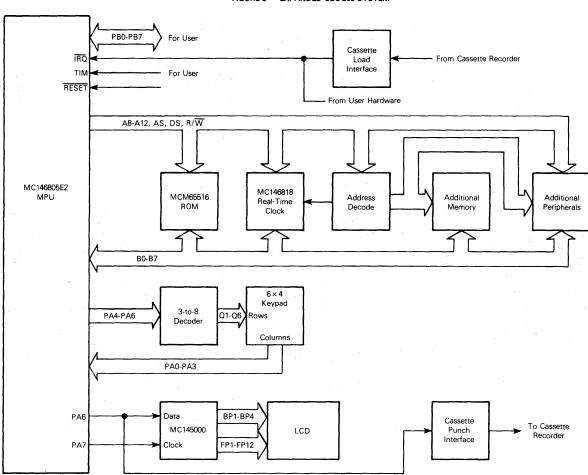

MCM68A332P2 — Sine/Cosine Look-Up Table MCM68364P35-3 — Log/Antilog Look-Up Table MCM65516P43M — MC146805 Monitor Program

4+5 volt for all read operations, except for programming, where +25 volts are required.

5Registered Outputs — 20 ns max clock to output 35 ns max address to clock setup time

6600 mil package

<sup>7</sup>Asynchronous register

8Synchronous register

9<sub>Typical access</sub>

## RAMS MOS DYNAMIC RAMS

| Organization | Part Number | Access Time<br>(ns Max) | Power<br>Supplies       | No. of<br>Pins |

|--------------|-------------|-------------------------|-------------------------|----------------|

|              |             |                         |                         |                |

| 16384 × 1    | MCM4116BP15 | 150                     | $+ 12, \pm 5 \text{ V}$ | 16             |

| 16384 × 1    | MCM4116BP20 | 200                     | + 12, ±5 V              | 16             |

| 16384 × 1    | MCM4116BP25 | 250                     | $+ 12, \pm 5$           | 16             |

| 16384 × 1    | MCM4517P10  | 100                     | +5 V                    | 16             |

| 16384 × 1    | MCM4517P12  | 120                     | +5 V                    | 16             |

| 16384 × 1    | MCM4517P15  | 150                     | +5 V                    | 16             |

| 65536 × 1    | MCM6665AP15 | 150                     | +5 V                    | 16             |

| 65536 × 1    | MCM6665AP20 | 200                     | +5 V                    | 16             |

| 65536 × 1    | MCM6665BP15 | 150                     | +5 V                    | 16             |

| 65536 × 1    | MCM6665BP20 | 200                     | +5 V                    | 16             |

| 262,144×1    | MCM6256P10* | 100                     | +5 V                    | 16             |

| 262,144×1    | MCM6256P12* | 120                     | +5 V                    | 16             |

| 262,144×1    | MCM6256P15* | 150                     | +5 V                    | 16             |

| 262,144×1    | MCM6257P10* | 100                     | +5 V                    | 16             |

| 262,144×1    | MCM6257P12* | 120                     | +5 V                    | 16             |

| 262,144×1    | MCM6257P15* | 150                     | +5 V                    | 16             |

## MOS STATIC RAMs (+5 Volts)

|              |             | Access Time | No. of |

|--------------|-------------|-------------|--------|

| Organization | Part Number | (ns max)    | Pins   |

| 128×8        | MCM6810     | 450         | 24     |

| 128×8        | MCM68A10    | 360         | 24     |

| 128×8        | MCM68B10    | 250         | 24     |

| 1024 × 4     | MCM2114P20  | 200         | 18     |

| 1024 × 4     | MCM2114P25  | 250         | 18     |

| 1024 × 4     | MCM2114P30  | 300         | 18     |

| 1024 × 4     | MCM2114P45  | 450         | 18     |

| 2048×8       | MCM2016HP45 | 45          | 24     |

| 2048×8       | MCM2016HN45 | 45          | 241    |

| 2048×8       | MCM2016HY45 | 45          | 241    |

| 2048×8       | MCM2016HP55 | . 55        | 24     |

| 2048×8       | MCM2016HN55 | 55          | 241    |

| 2048×8       | MCM2016HY55 | 55          | 241    |

| 2048×8       | MCM2016HP70 | 70          | 24     |

| 2048×8       | MCM2016HN70 | 70          | 241    |

| 2048 × 8     | MCM2016HY70 | 70          | 241    |

| 16384 × 1    | MCM2167HP35 | 35          | 20     |

| 16384 × 1    | MCM2167HL35 | 35          | 20     |

| 16384 × 1    | MCM2167HZ35 | 35          | 20     |

| 16384 × 1    | MCM2167HP45 | 45          | 20     |

| 16384 × 1    | MCM2167HL45 | 45          | 20     |

| 16384 × 1    | MCM2167HZ45 | 45          | 20     |

| 16384 × 1    | MCM2167HP70 | • 70        | 20     |

| 16384 × 1    | MCM2167HL70 | 70          | 20     |

| 16384 × 1    | MCM2167HZ70 | 70          | 20     |

# RAMs (Continued)

## CMOS STATIC RAMs (+5 Volts)

| Organization | Part Number  | Access Time<br>(ns max) | No. of<br>Pins |

|--------------|--------------|-------------------------|----------------|

| 4096×1       | MCM6147P55   | 55                      | 18             |

| 4096 × 1     | MCM6147P70   | 70                      | 18             |

| 4096 × 1     | MCM61L47P55  | 55                      | 18             |

| 4096 × 1     | MCM61L47P70  | 70                      | 20             |

| 4096 × 4     | MCM6168HP35* | 35                      | 20             |

| 4096×4       | MCM6168HP45* | 45                      | 20             |

| 4096×4       | MCM6168HP55* | 55                      | 20             |

| 4096 × 4     | MCM6169HP35* | 35                      | 22             |

| 4096 × 4     | MCM6169HP45* | 45                      | 22             |

| 4096×4       | MCM6169HP55* | 55                      | 22             |

| 2048 × 8     | MCM6116P12   | 120                     | 24             |

| 2048×8       | MCM6116P15   | 150                     | 24             |

| 2048×8       | MCM6116P20   | 200                     | 24             |

| 2048 × 8     | MCM61L16P12  | 120                     | 24             |

| 2048×8       | MCM61L16P15  | 150                     | 24             |

| 2048 × 8     | MCM61L16P20  | 200                     | 24             |

## ECL 10K, 10KH RAMs (Open Emitter)

|              |              | Access Time |       |

|--------------|--------------|-------------|-------|

| Organization | Part Number  | (ns max)    | Pins  |

|              |              |             | FIIIS |

| 8×2          | MCM10143     | 15.5        | 24    |

| 16×4         | MC10H145     | 6           | . 16  |

| 16×4         | MCM10145     | 15          | - 16  |

| 64×1         | MCM10148     | 15          | 16    |

| 128 × 1      | MCM10147     | 15          | 16    |

| 256 × 1      | MCM10144     | 26          | 16    |

| 256 × 1      | MCM10152     | 15          | 16    |

| 1024 × 1     | MCM10146     | 29          | 16    |

| 1024 × 1     | MCM10415-20  | 20          | 16    |

| 1024 × 1     | MCM10415-15  | 15          | 16    |

| 1024×1       | MCM10415-10* | 10          | 16    |

| 256 × 4      | MCM10422-15* | 15          | 24    |

| 256 × 4      | MCM10422-10* | 10          | 24    |

| 4096×1       | MCM10470-25* | 25          | 18    |

| 4096×1       | MCM10470-15* | · 15        | 18    |

| 1024 × 4     | MCM10474-25* | 25          | 24    |

| 1024×4       | MCM10474-15* | 15          | 24    |

| 16384×1      | MCM10480-20* | 20          | - 20  |

| 4096×4       | MCM10484-20* | 20          | 28    |

# RAMs (Continued)

## ECL 100K RAMs (Open Emitter)

| Organization | Part Number   | Access Time<br>(ns max) | Pins |

|--------------|---------------|-------------------------|------|

| 1024 × 1     | MCM100415-10* | 10                      | 16   |

| 256 × 4      | MCM100422-10* | 10                      | 24   |

| 4096 × 1     | MCM100470-15* | 15                      | 18   |

| 1024 × 4     | MCM100474-15* | 15                      | 24   |

| 16384 × 1    | MCM100480-20* | - 20                    | 20   |

| 4096 × 4     | MCM100484-20* | 20                      | 28   |

## TTL RAMs

| Organization | Part Number | Access Time (ns max) | Output  | No. of<br>Pins |

|--------------|-------------|----------------------|---------|----------------|

| 1024 × 1     | MCM93415    | 45                   | O.C.    | 16             |

| 1024 × 1     | MCM93425    | 45                   | 3-State | 16             |

| 256×4        | MCM93L422   | 60                   | 3-State | 22             |

| 256 × 4      | MCM93L422A  | 45                   | 3-Sţate | 22             |

| 256 × 4      | MCM93422    | 45                   | 3-State | 22             |

| 256 × 4      | MCM93422A   | 35                   | 3-State | 22             |

# **ROMs**

## MOS CHARACTER GENERATORS<sup>2</sup> (+5 Volts)

| Organization         | Part Number | Access Time<br>(ns max) | No. of<br>Pins |

|----------------------|-------------|-------------------------|----------------|

| 128 × (7 × 5)        | MCM6670P    | 350                     | 18             |

| 128 × (7 × 5)        | MCM6674P    | 350                     | 18             |

| 128 × (9 × 7)        | MCM66700P   | 350                     | 24             |

| 128 × (9 × 7)        | MCM66710P   | 350                     | 24             |

| 128 × (9 × 7)        | MCM66714P   | 350                     | 24             |

| 128×(9×7)            | MCM66720P   | 350                     | 24             |

| .128 × (9 × 7)       | MCM66730P   | 350                     | 24             |

| 128 × (9 × 7)        | MCM66734P   | 350                     | 24             |

| 128 × (9 × 7)        | MCM66740P   | 350                     | 24             |

| 128 × (9 × 7)        | MCM66750P   | 350                     | 24             |

| 128×(9×7)            | MCM66760P   | 350                     | 24             |

| 128×(9×7)            | MCM66770P   | 350                     | 24             |

| $128 = (9 \times 7)$ | MCM66780P   | 350                     | 24             |

| 128×(9×7)            | MCM66790P   | 350                     | 24             |

# ROMs (Continued)

## MOS Binary ROMs (+5 Volts)

| :            |                            | Access Time | No. of |

|--------------|----------------------------|-------------|--------|

| Organization | Part Number                | (ns max)    | Pins   |

| 2048 × 8     | MCM68A316EP                | 350         | 24     |

| 2048×8       | MCM68A316EP91 <sup>3</sup> | 350         | 24     |

| 4096 × 8     | MCM68A332P                 | 350         | 24     |

| 4096 × 8     | MCM68A332P2 <sup>3</sup>   | 350         | 24     |

| 8192×8       | MCM68364P20                | 200         | 24     |

| 8192×8       | MCM68364P25                | 250         | 24     |

| 8192×8       | MCM68364P35                | 350         | 24     |

| 8192×8       | MCM68364P35-3 <sup>3</sup> | 350         | 24     |

| 8192×8       | MCM68365P25                | 250         | 24     |

| 8192×8       | MCM68365P35                | 350         | 24     |

| 8192×8       | MCM68366P25                | 250         | 24     |

| 8192×8       | MCM68366P35                | 350         | 24     |

| 8192×8       | MCM68367P                  | 450         | 24     |

| 8192×8       | MCM68368P                  | 450         | 24     |

| 8192×8       | MCM68369P20                | 200         | - 28   |

| 8192×8       | MCM68369P25                | 250         | 28     |

| 8192×8       | MCM68369P30                | 300         | 28     |

| 8192×8       | MCM68370P20                | 200         | 28     |

| 8192×8       | MCM68370P25                | 250         | 28     |

| 8192×8       | MCM68370P30                | 300         | 28     |

| 8192 × 10    | MCM68380P                  | 3009        | 24     |

| 16384 × 8    | MCM63128P15                | 150         | 28     |

| 16384×8      | MCM63128P20                | 200         | 28     |

| 32768×8      | MCM63256P15                | 150         | 28     |

| 32768 × 8    | MCM63256P20                | 200         | 28     |

## CMOS ROMs (+5 Volts)

| Organization | Part Number               | Access Time<br>(ns max) | No. of<br>Pins |

|--------------|---------------------------|-------------------------|----------------|

| 2048×8       | MCM65516P43               | 430                     | 18             |

| 2048 × 8     | MCM65516P43M <sup>3</sup> | 430                     | 18             |

| 2048×8       | MCM65516P55               | 550                     | 18             |

| 32768×8      | MCM65256P35               | 350                     | 28             |

## **EPROMs**

## **MOS EPROMs**

| Organization | Part Number | Access Time (ns max) | Power<br>Supplies <sup>4</sup> | No. of<br>Pins |

|--------------|-------------|----------------------|--------------------------------|----------------|

| 8192×8       | MCM68764C35 | 350                  | +5 V, 25 V                     | 24             |

| 8192×8       | MCM68764C   | 450                  | +5 V, 25 V                     | . 24           |

| 8192×8       | MCM68766C30 | 300                  | +5 V, 25 V                     | 24             |

| 8192×8       | MCM68766C35 | 350                  | +5 V, 25 V                     | 24             |

| 8192×8       | MCM68766C40 | 400                  | +5 V, 25 V                     | 24             |

| 8192×8       | MCM68766C   | 450                  | +5 V, 25 V                     | 24             |

## ROM/EEPROMs

## MOS

| Organization |                 | Organization |          | No. of |

|--------------|-----------------|--------------|----------|--------|

| ROM          | EEPROM          | Part Number  | (ns max) | Pins   |

| 14K×8        | 2K×8            | MCM6836E16   | 270      | 28     |

| 14K×8        | 2K × 8 plus 256 |              | 270      | 28     |

|              | redundant bytes |              |          |        |

## **DUAL-PORT RAM**

## MOS

|              |             | Access Time | No. of |

|--------------|-------------|-------------|--------|

| Organization | Part Number | (ns max)    | Pins   |

| 256×8        | MCM68HC34*  | 240         | 40     |

# **PROMs**

## **ECL PROMs**

| Organization | Part Number | Access Time<br>(ns max) | No. of<br>Pins |

|--------------|-------------|-------------------------|----------------|

| 32×8         | MCM10139    | 20                      | 16             |

| 256×4        | MCM10149    | 25                      | 16             |

| 256×4        | MCM10149A*  | 15                      | . 16           |

## TTL PROMs (3-State Outputs)

|              | <del> </del>             | Access Time | No. of |

|--------------|--------------------------|-------------|--------|

| Organization | Part Number              | (ns max)    | Pins   |

| 32×8         | MCM27S19*                | 25          | 16     |

| 512×4        | MCM7621                  | 70          | 16     |

| 512×4        | MCM7621A                 | 60          | 16     |

| 5.12×8       | MCM7641                  | 70          | 24     |

| 512×8        | MCM7641A                 | 60          | 24     |

| 512×8        | MCM7649                  | 60          | 20     |

| 512×8        | MCM7649A                 | 50          | 20     |

| 512×8        | MCM27S29A*               | 35          | 20     |

| 512×8        | MCM27S31A*               | 35          | 24     |

| 512×8        | MCM27S25A*               | See Note 5  | 24     |

| 512×8        | MCM27S27A*               | See Note 5  | , 22   |

| 1024 × 4     | MCM7643                  | 70          | 18     |

| 1024 × 4     | MCM7643A                 | 50          | 18     |

| 1024×8       | MCM7681                  | 70          | 24     |

| 1024×8       | MCM7681A                 | 50          | 24     |

| 1024×8       | MCM27S181*               | 35          | 246    |

| 1024×8       | MCM27S281*               | 35          | 241    |

| 1024×8       | MCM27S35A <sup>7</sup> * | See Note 5  | 24     |

| 1024×8       | MCM27S37A <sup>8</sup> * | See Note 5  | 24     |

| 2048×4       | MCM7685                  | 70          | 18     |

| 2048 × 4     | MCM7685A                 | 55          | 18     |

| 2048×8       | MCM76161                 | 70          | 24     |

| 2048×8       | MCM76161A                | 60.         | 24     |

| 2048×8       | MCM27S191*               | 35          | 246    |

| 2048×8       | MCM27S291*               | 35          | 241    |

| 2048×8       | MCM27S45A* <sup>7</sup>  | See Note 5  | 24     |

| 2048×8       | MCM27S47A*8              | See Note 5  | 24     |

| 4096×4       | MCM76165                 | 50          | 20     |

| 4096 × 4     | MCM76165A                | 35          | 20     |

## **BUBBLE**

| Organization  | Part Number | Access Time<br>(Average) | No. of<br>Pins |  |

|---------------|-------------|--------------------------|----------------|--|

| 262,144 × 1   | MBM2256     | 7.0 ms                   | 16             |  |

| 1,048,576 × 1 | MBM2011A    | 11.5 ms                  | 16             |  |

## MOS Dynamic RAMs

### 16.384-BIT DYNAMIC RANDOM ACCESS MEMORY

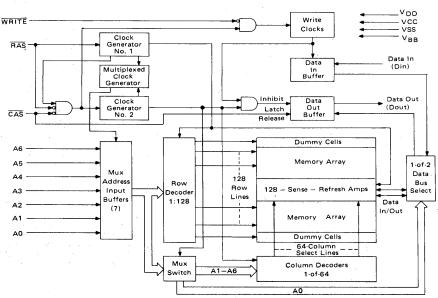

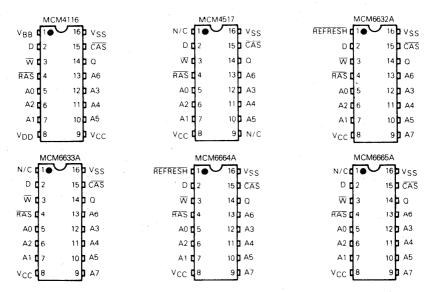

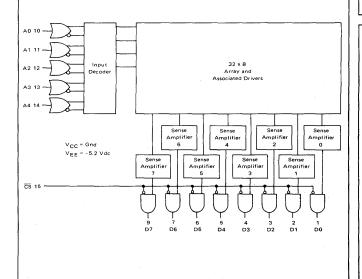

The MCM4116B is a 16,384-bit, high-speed dynamic Random Access Memory designed for high-performance, low-cost applications in mainframe and buffer memories and peripheral storage. Organized as 16,384 one-bit words and fabricated using Motorola's highly reliable N-channel double-polysilicon technology, this device optimizes speed, power, and density tradeoffs.

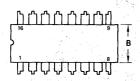

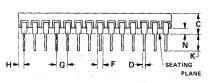

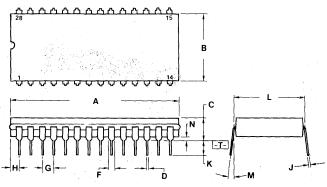

By multiplexing row and column address inputs, the MCM4116B requires only seven address lines and permits packaging in Motorola's standard 16-pin dual in-line packages. This packaging technique allows high system density and is compatible with widely available automated test and insertion equipment. Complete address decoding is done on chip with address latches incorporated.

All inputs are TTL compatible, and the output is 3-state TTL compatible. The data output of the MCM4116B is controlled by the column address strobe and remains valid from access time until the column address strobe returns to the high state. This output scheme allows higher degrees of system design flexibility such as common input/output operation and two dimensional memory selection by decoding both row address and column address strobes.

The MCM4116B incorporates a one-transistor cell design and dynamic storage techniques, with each of the 128 row addresses requiring a refresh cycle every 2 milliseconds.

- Flexible Timing with Read-Modify-Write, RAS-Only Refresh, and Page-Mode Capability

- Industry Standard 16-Pin Package

- 16,384 X 1 Organization

- ±10% Tolerance on All Power Supplies

- All Inputs are Fully TTL Compatible

- Three-State Fully TTL-Compatible Output

- Common I/O Capability When Using "Early Write" Mode

- On-Chip Latches for Addresses and Data In

- Low Power Dissipation 426 mW Active, 20 mW Standby (Max)

- Fast Access Time Options:150 ns MCM4116BP-15, BC-15

200 ns MCM4116BP-20, BC-20

250 ns MCM4116BP-25, BC-25

300 ns MCM4116BP-30, BC-30

- Easy Upgrade from 16-Pin 4K RAMs

## ABSOLUTE MAXIMUM RATINGS (See Note 1)

| Rating                             | Symbol                            | Value       | Unit |

|------------------------------------|-----------------------------------|-------------|------|

| Voltage on Any Pin Relative to VBB | V <sub>in</sub> ,V <sub>out</sub> | -0.5 to +20 | Vdc  |

| Operating Temperature Range        | TA                                | 0 to +70    | °C   |

| Storage Temperature Range          | T <sub>stg</sub>                  | -65 to +150 | °C   |

| Power Dissipation                  | PD                                | 1.0         | w    |

| Data Out Current                   | lout                              | 50          | mA   |

NOTE 1: Permanent device damage may occur if ABSOLUTE MAXIMUM RAT-INGS are exceeded. Functional operation should be restricted to RECOM-MENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

## MCM4116B

## MOS

(N-CHANNEL)

16,384-BIT DYNAMIC RANDOM ACCESS MEMORY

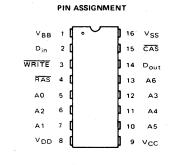

#### PIN NAMES A0-A6 Address Inputs CAS Column Address Strobe Din Data In Dout BAS Data Out Row Address Strobe WRITE Read/Write Input Power (-5 V) $V_{BB}$ Power (+5 V) Vcc Power (+12 V) VDD Ground

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

### DC OPERATING CONDITIONS AND CHARACTERISTICS (Full operating voltage and temperature range unless otherwise noted.)

#### RECOMMENDED OPERATING CONDITIONS

| Parameter                                          | Symbol          | Min  | Тур  | Max  | Unit | Notes |

|----------------------------------------------------|-----------------|------|------|------|------|-------|

| Supply Voltage                                     | V <sub>DD</sub> | 10.8 | 12.0 | 13.2 | Vdc  | 1     |

|                                                    | Vcc             | 4.5  | 5.0  | 5.5  | Vdc  | 1, 2  |

|                                                    | V <sub>SS</sub> | 0    | - 0  | 0    | Vdc  | 1     |

|                                                    | V <sub>BB</sub> | -4.5 | -5.0 | -5.5 | Vdc  | 1     |

| Logic 1 Voltage, RAS, CAS, WRITE                   | VIHC            | 2.4  | -    | 7.0  | Vdc  | 1     |

| Logic 1 Voltage, all inputs except RAS, CAS, WRITE | VIH             | 2.4  | - 1  | 7.0  | Vdc  | 1     |

| Logic 0 Voltage, all inputs                        | VIL             | -1.0 | _    | 0.8  | Vdc  | 1     |

DC CHARACTERISTICS ( $V_{DD} = 12 \text{ V} \pm 10\%$ ,  $V_{CC} = 5.0 \text{ V} \pm 10\%$ ,  $V_{RR} = -5.0 \text{ V} \pm 10\%$ ,  $V_{SS} = 0 \text{ V}$ ,  $T_A = 0 \text{ to } 70^{\circ}\text{C.}$ )

| Characteristic                                                        | Symbol             | Min | Max  | Units | Notes |

|-----------------------------------------------------------------------|--------------------|-----|------|-------|-------|

| Average V <sub>DD</sub> Power Supply Current                          | I <sub>DD1</sub>   | _   | 35   | mA    | 4     |

| V <sub>CC</sub> Power Supply Current                                  | ¹cc                | -   | -    | mA    | 5     |

| Average VBB Power Supply Current                                      | <sup>I</sup> BB1,3 | -   | 200  | μА    |       |

| Standby V <sub>BB</sub> Power Supply Current                          | I <sub>BB2</sub>   | _   | 100  | μА    |       |

| Standby V <sub>DD</sub> Power Supply Current                          | I <sub>DD2</sub>   | _   | 1.5  | mA    | 6     |

| Average V <sub>DD</sub> Power Supply Current during "RAS only "cycles | IDD3               | -   | 27   | mA    | 4     |

| Input Leakage Current (any input)                                     | ۱۱(L)              | -   | . 10 | μΑ    |       |

| Output Leakage Current                                                | <sup>1</sup> O(L)  | -   | 10   | μА    | 6,7   |

| Output Logic 1 Voltage @ I <sub>out</sub> = -5 mA                     | Voн                | 2.4 | -    | Vdc   | 2     |

| Output Logic 0 Voltage @ I <sub>out</sub> = 4.2 mA                    | VOL                | -   | 0.4  | Vdc   |       |

#### NOTES:

- 1. All voltages referenced to  $V_{SS}$ ,  $V_{BB}$  must be applied before and removed after other supply voltages.

- 2. Output voltage will swing from VSS to VCC under open circuit conditions. For purposes of maintaining data in power-down mode, VCC may be reduced to VSS without affecting refresh operations. VOH(min) specification is not guaranteed in this mode.

- 3. Several cycles are required after power-up before proper device operation is achieved. Any 8 cycles which perform refresh are adequate.

- 4. Current is proportional to cycle rate; maximum current is measured at the fastest cycle rate.

- 5. I<sub>CC</sub> depends upon output loading. The V<sub>CC</sub> supply is connected to the output buffer only.

6. Output is disabled (open-circuit) when CAS is at a logic 1.

- 7. 0 V  $\leq$  V out  $\leq$  +5.5 V. 7.  $0.0 \le V_{\text{out}} \le +5.5 \text{ V}$ .

8. Capacitance measured with a Boonton Meter or effective capacitance calculated from the equation:  $C = \frac{1\Delta_t}{\Delta V}$

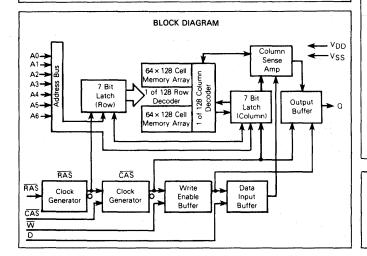

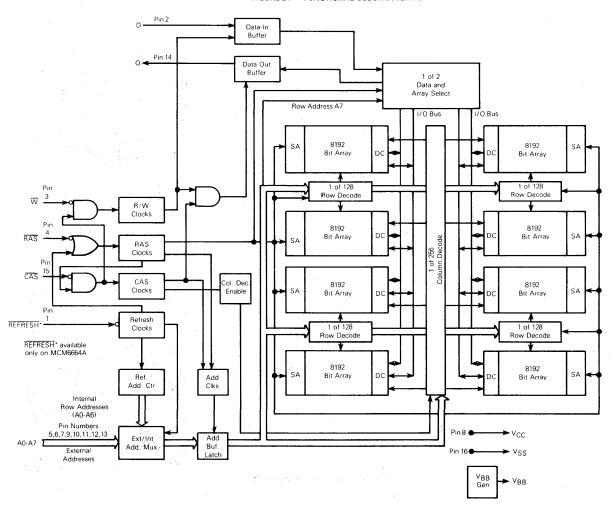

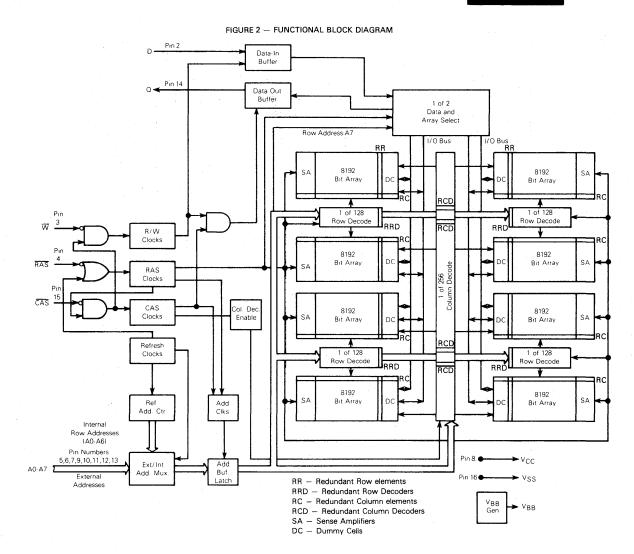

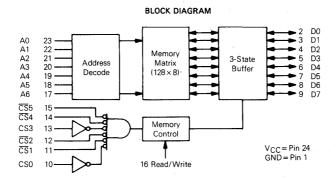

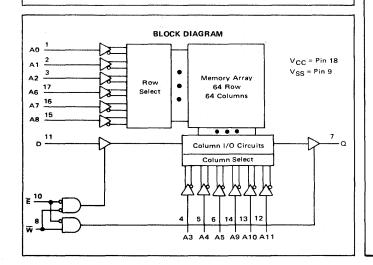

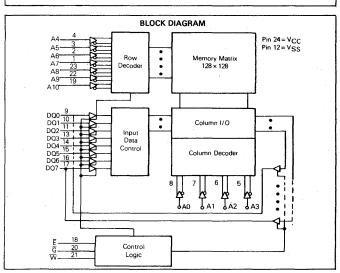

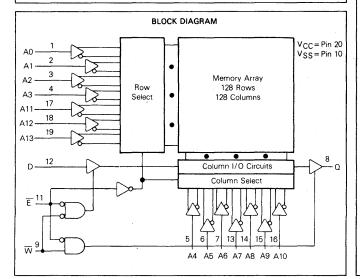

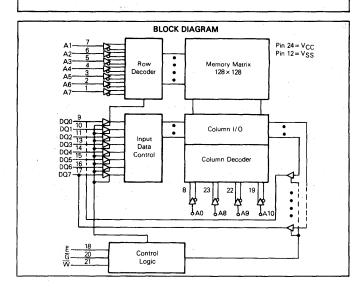

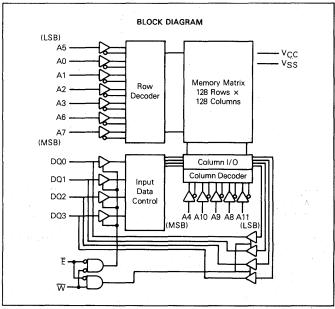

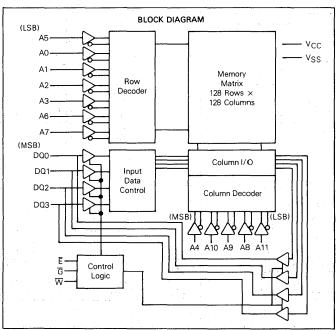

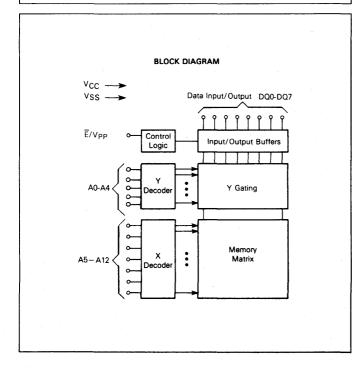

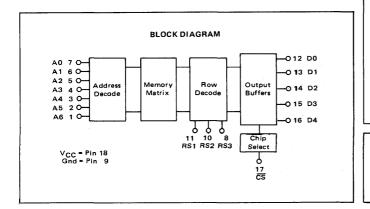

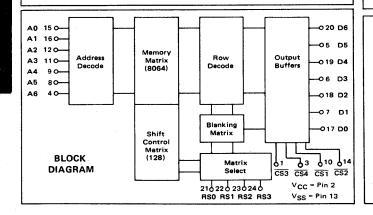

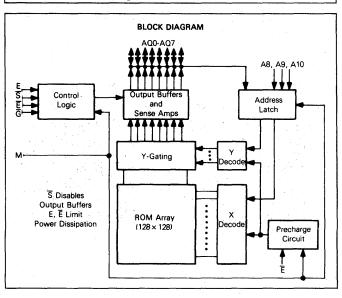

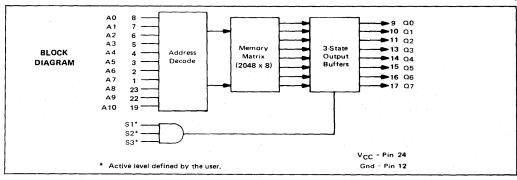

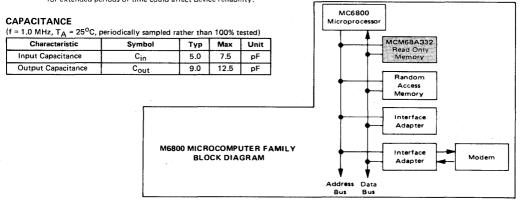

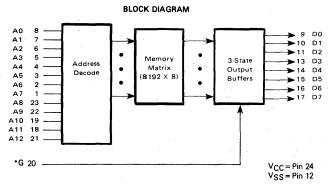

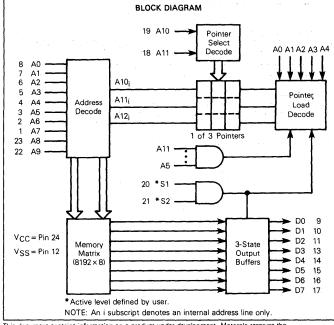

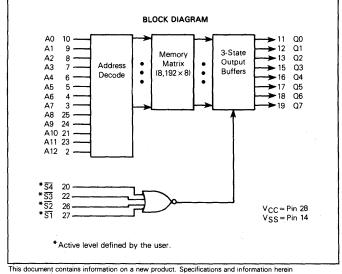

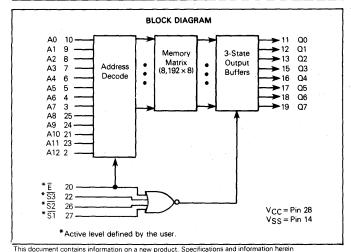

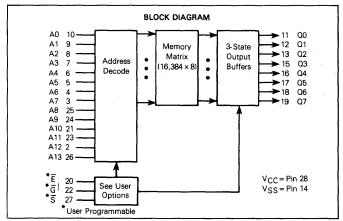

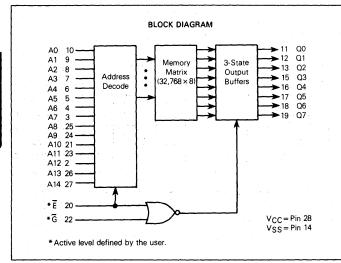

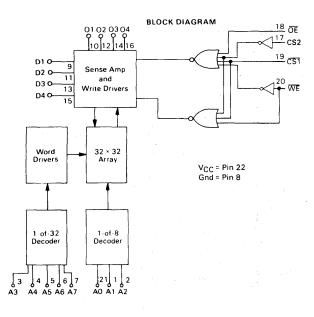

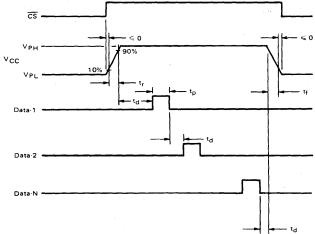

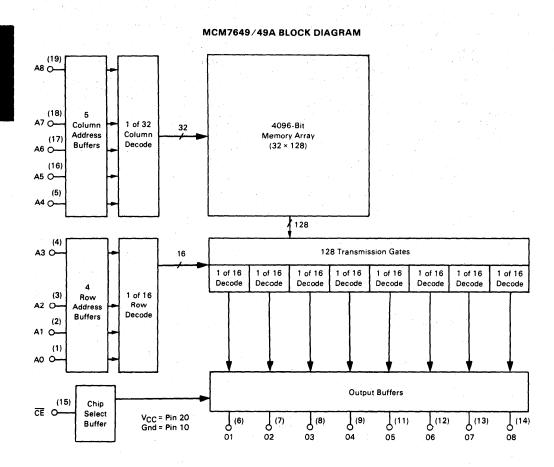

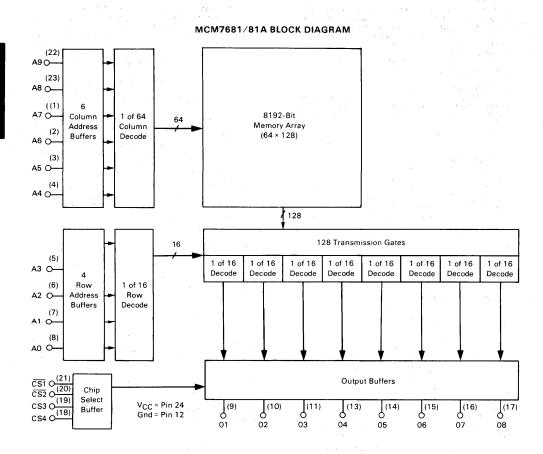

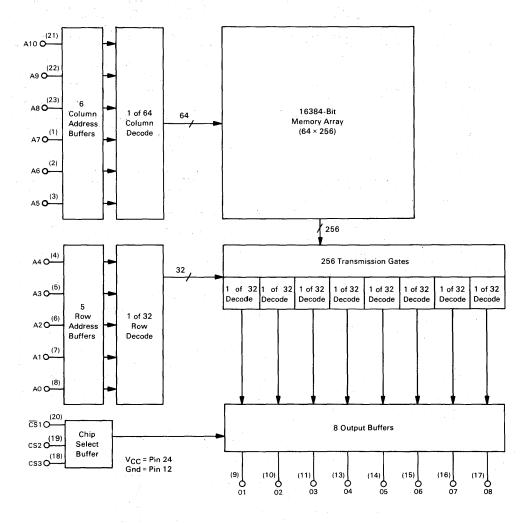

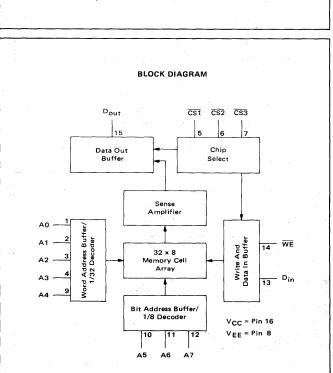

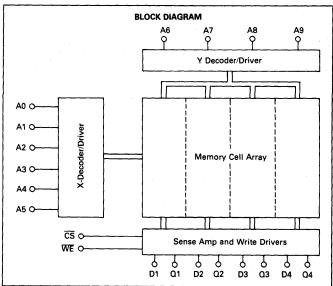

### **BLOCK DIAGRAM**

Units

ρF

рF

ρF

Notes

9

9

7,9

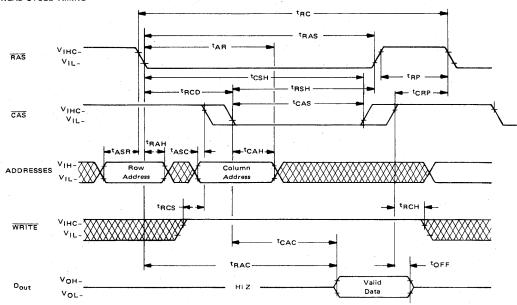

## AC OPERATING CONDITIONS AND CHARACTERISTICS (See Notes 3, 9, 14) (Read, Write, and Read-Modify-Write Cycles)

#### RECOMMENDED AC OPERATING CONDITIONS

$(V_{DD} = 12 \text{ V} \pm 10\%, V_{CC} = 5.0 \text{ V} \pm 10\%, V_{BB} = -5.0 \text{ V} \pm 10\%, V_{SS} = 0 \text{ V}, T_{\Delta} = 0 \text{ to } 70^{\circ}\text{C.})$

|                                               |                  | MCM4 | 116B-15 | мсм4 | 116B-20    | MCM41 | 16B-25 | MCM4 | 116B-30 |       |        |

|-----------------------------------------------|------------------|------|---------|------|------------|-------|--------|------|---------|-------|--------|

| Parameter                                     | Symbol           | Min  | Max     | Min  | Max        | Min   | Max    | Min  | Max     | Units | Notes  |

| Random Read or Write Cycle Time               | tRC              | 375  | _       | 375  | -          | 410   | -      | 480  | -       | ns    |        |

| Read Write Cycle Time                         | tRWC             | 375  | _       | 375  | -          | 515   | _      | 660  | -       | ns    |        |

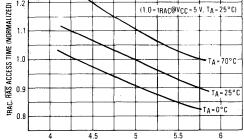

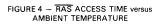

| Access Time from Row Address Strobe           | tRAC             | -    | 150     | -    | 200        | -     | 250    |      | 300     | ns    | 10, 12 |

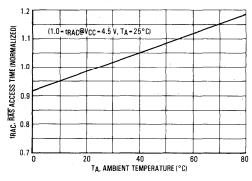

| Access Time from Column Address Strobe        | tCAC             | -    | 100     | -    | 135        |       | 165    |      | 200     | ns    | 11, 12 |

| Output Buffer and Turn-off Delay              | tOFF             | 0    | 50      | 0    | 50         | 0     | 60     | 0    | 60      | ns    | 17     |

| Row Address Strobe Precharge Time             | tRP              | 100  | -       | 120  | -          | 150   | -      | 180  | -       | ns    |        |

| Row Address Strobe Pulse Width                | tRAS             | 150  | 10,000  | 200  | 10,000     | 250   | 10,000 | 300  | 10,000  | ns    |        |

| Column Address Strobe Pulse Width             | tCAS             | 100  | 10,000  | 135  | 10,000     | 165   | 10,000 | 200  | 10,000  | ns    |        |

| Row to Column Strobe Lead Time                | tRCD             | 20   | 50      | 25   | <b>6</b> 5 | 35    | 85     | 60   | 100     | ns    | 13     |

| Row Address Setup Time                        | tASR             | 0    | -       | 0    | _          | 0     | _      | 0    | -       | ns    |        |

| Row Address Hold Time                         | <sup>t</sup> RAH | 20   | _       | 25   | _          | 35    | -      | 60   | -       | ns    |        |

| Column Address Setup Time                     | tASC             | -10  |         | -10  | _          | -10   | _      | -10  | -       | ns    |        |

| Column Address Hold Time                      | tCAH             | 45   | _       | 55   | _          | 75    | -      | 100  | -       | ns    |        |

| Column Address Hold Time<br>Referenced to RAS | <sup>t</sup> AR  | 95   | -       | 120  | _          | 160   | -      | 200  | -       | ns    |        |

| Transition Time (Rise and Fall)               | t <sub>T</sub>   | 3.0  | 35      | 3.0  | 50         | 3.0   | 50     | 3.0  | 50      | ns    | 14     |

| Read Command Setup Time                       | tRCS             | 0    | -       | 0    | _          | 0     |        | 0    | -       | ns    |        |

| Read Command Hold Time                        | <sup>t</sup> RCH | 0    |         | 0    | -          | 0     | _      | 0    | _       | ns    |        |

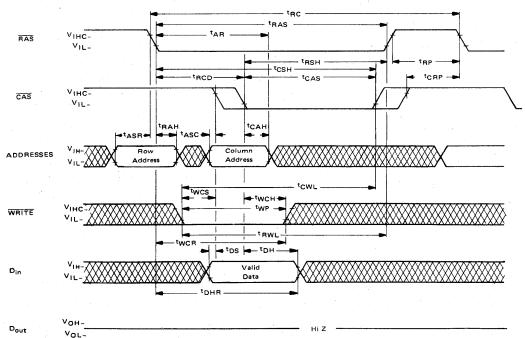

| Write Command Hold Time                       | tWCH             | 45   | T -     | 55   | _          | 75    | -      | 100  | _       | ns    |        |

| Write Command Hold Time<br>Referenced to RAS  | twcr             | 95   | -       | 120  | _          | 160   | _      | 200  |         | ns    |        |

| Write Command Pulse Width                     | twp              | 45   | -       | 55   | _          | 75    | -      | 100  | -       | ns .  |        |

| Write Command to Row Strobe Lead Time         | <sup>t</sup> RWL | 60   | -       | 80   | -          | 100   |        | 180  |         | ns    | Ī .    |

| Write Command to Column Strobe<br>Lead Time   | tCWL             | 60   | -       | 80   | -          | 100   | -      | 180  | -       | ns    |        |

| Data in Setup Time                            | tDS              | 0    | -       | 0    | -          | 0     | _      | 0    | _       | ns    | 15     |

| Data in Hold Time                             | tDH              | 45   | -       | 55   |            | 75    |        | 100  | -       | ns    | 15     |

| Data in Hold Time Referenced to RAS           | <sup>t</sup> DHR | 95   | -       | 120  | -          | 160   | _      | 200  | -       | ns    |        |

| Column to Row Strobe Precharge Time           | tCRP             | -20  | -       | -20  |            | -20   |        | -20  | -       | ns    |        |

| RAS Hold Time                                 | tRSH             | 100  | -       | 135  | s -        | 165   | _      | 200  | -       | ns    |        |

| Refresh Period                                | tRFSH            |      | 2.0     | _    | 2.0        |       | 2.0    | -    | 2.0     | ms    |        |

| WRITE Command Setup Time                      | twcs             | -20  |         | -20  | _          | -20   |        | -20  |         | ns    |        |

| CAS to WRITE Delay                            | tCWD             | 70   |         | 95   |            | 125   |        | 180  |         | ns    | 16     |

| RAS to WRITE Delay                            | tRWD             | 120  |         | 160  | -          | 210   | -      | 280  |         | ns    | 16     |

| CAS Precharge Time (Page mode cycle only)     | <sup>t</sup> CP  | 60   | T -     | 80   |            | . 100 | -      | 100  | -       | ns    |        |

| Page Mode Cycle Time                          | tPC              | 170  |         | 225  | _          | 275   | -      | 325  |         | ns    |        |

| CAS Hold Time                                 | tCSH             | 150  | _       | 200  | _          | 250   | _      | 300  | -       | ns    |        |

| NOTES:  | (continued) |

|---------|-------------|

| NO LEG. | (Continueu) |

- 9. AC measurements assume  $t_T = 5.0$  ns.

- 10. Assumes that  $t_{RCD} + t_T \le t_{RCD}$  (max).

- 11. Assumes that  $t_{RCD} + t_{T} \ge t_{RCD}$  (max).

- 12. Measured with a load circuit equivalent to 2 TTL loads and 100 pF.

- 13. Operation within the t<sub>RCD</sub> (max) limit ensures that t<sub>RAC</sub> (max) can be met. t<sub>RCD</sub> (max) is specified as a reference point only; if t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub> (max) limit, then access time is controlled exclusively by t<sub>CAC</sub>.

Parameter

Input Capacitance RAS, CAS, WRITE

Input Capacitance (A0-A5), Din

Output Capacitance (Dout)

Symbol

C<sub>11</sub>

$C_{12}$

$C_{o}$

Тур

4.0

8.0

5.0

Max

5.0

10

7.0

- 14. VIHC (min) or VIH (min) and VIL (max) are reference levels for measuring timing of input signals. Also, transistion times are measured between VIHC or VIH and VIL.

- 15. These parameters are referenced to CAS leading edge in random write cycles and to WRITE leading edge in delayed write or read-modify-write cycles.

- 16. tWCS, t<sub>CWD</sub> and t<sub>RWD</sub> are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only: If twCS > twCS (min), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout the entire cycle; If t<sub>CWD</sub> > t<sub>CWD</sub> (min) and t<sub>RWD</sub> > t<sub>RWD</sub> (min), the cycle is a read-write cycle and the data out will contain data read from the selected cell; If neither of the above sets of conditions is satisfied the condition of the data out (at access time) is indeterminate.

- 17. Assumes that tCRP > 50 ns.

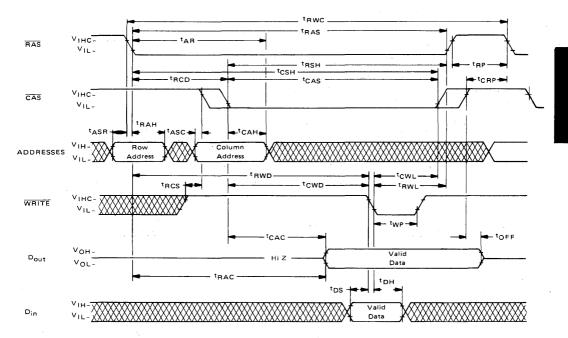

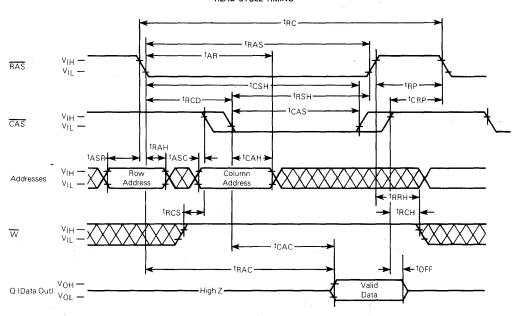

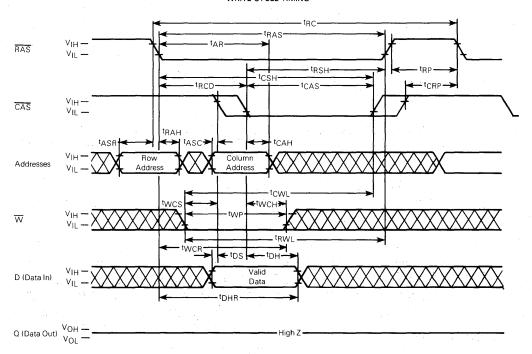

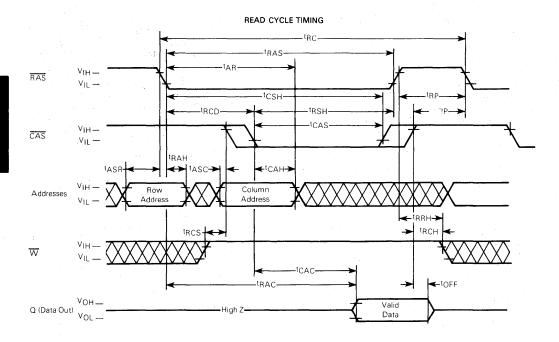

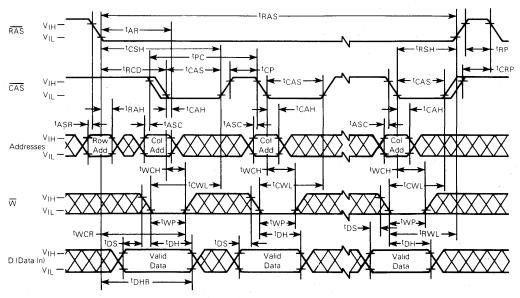

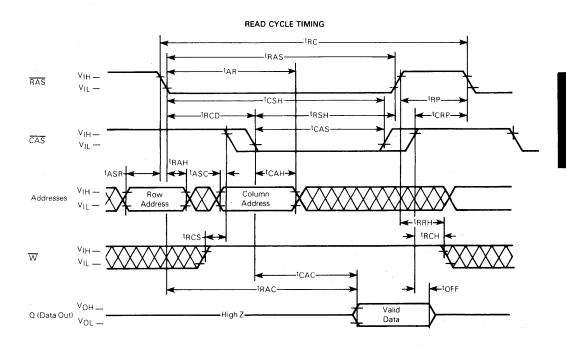

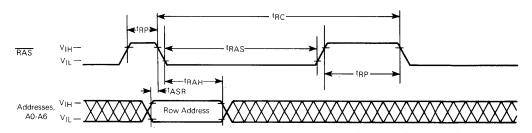

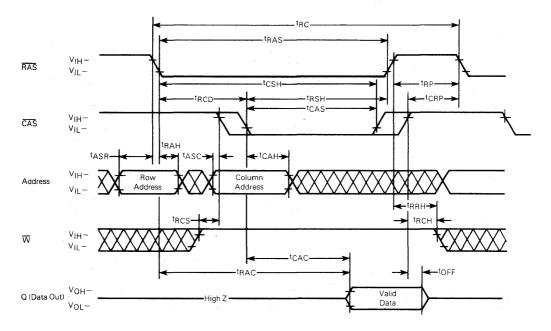

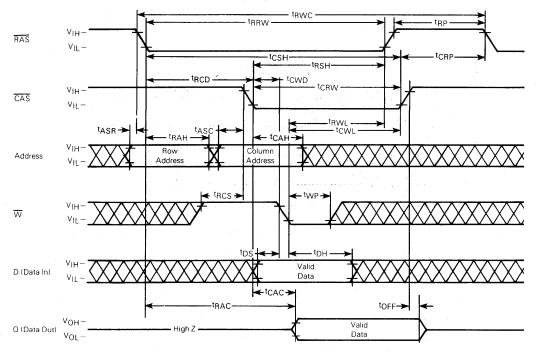

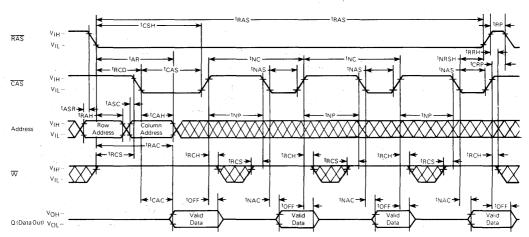

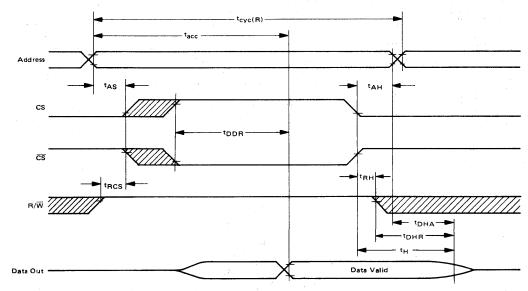

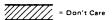

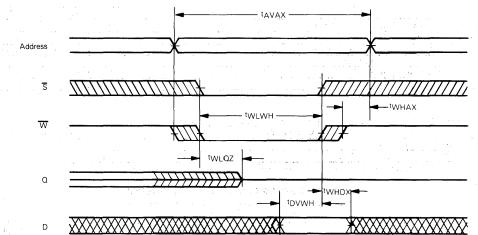

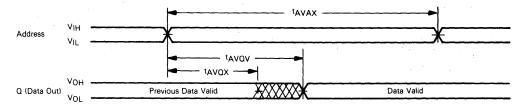

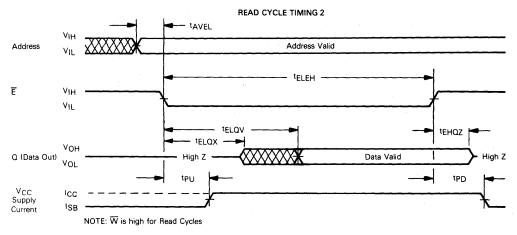

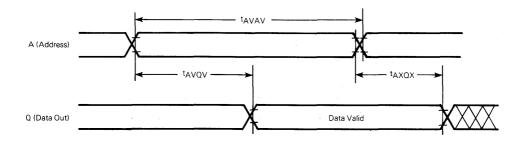

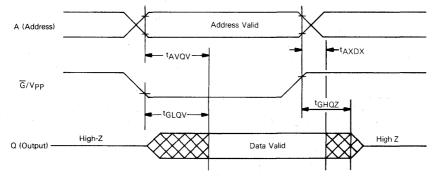

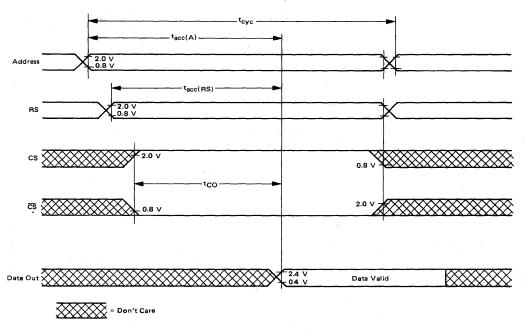

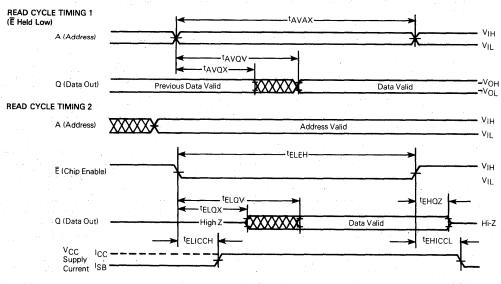

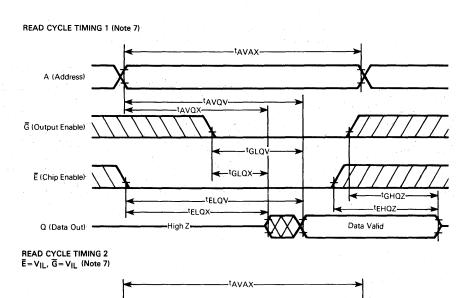

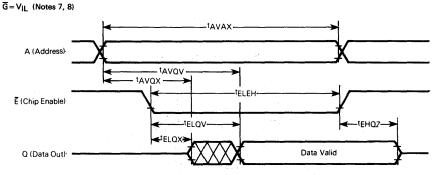

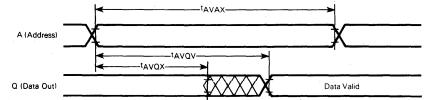

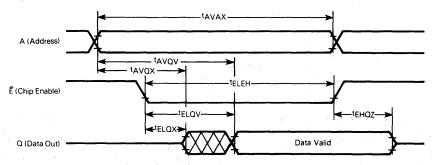

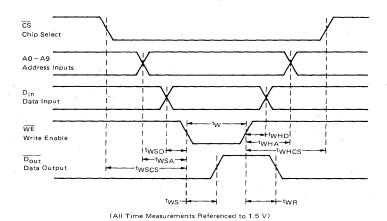

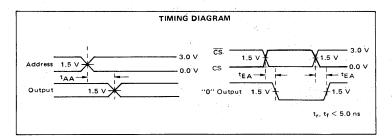

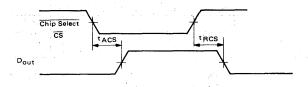

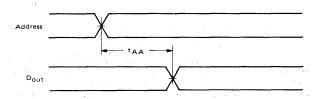

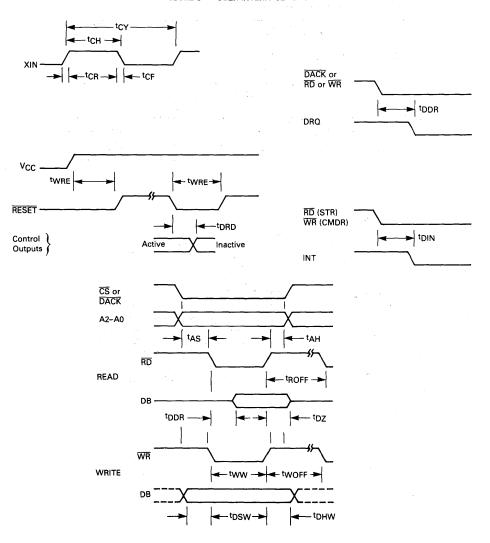

### READ CYCLE TIMING

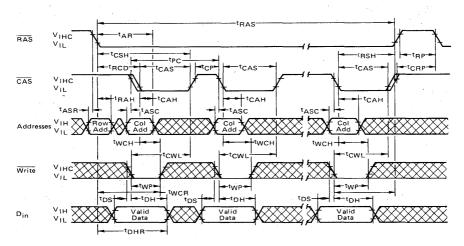

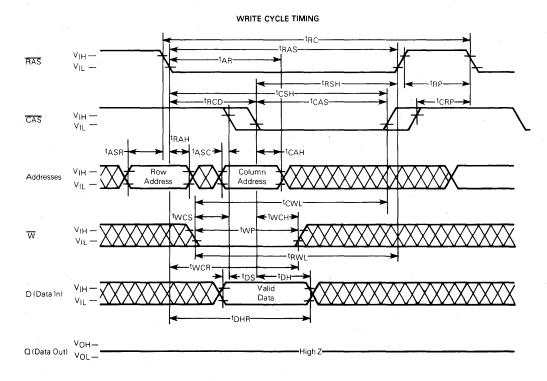

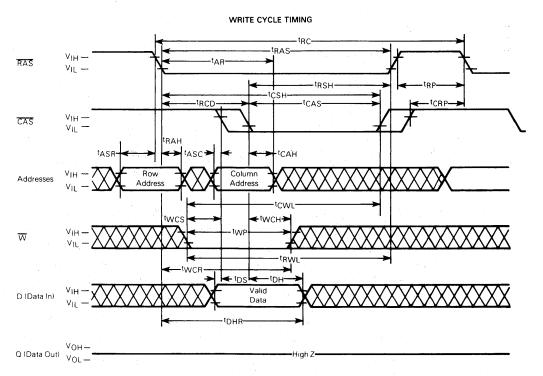

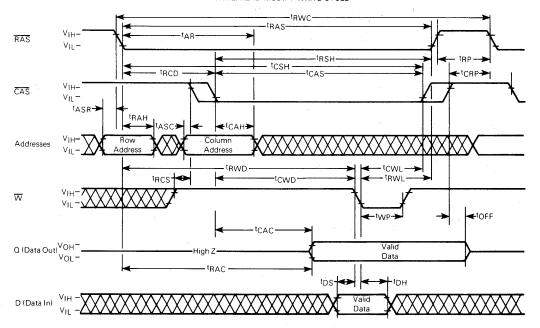

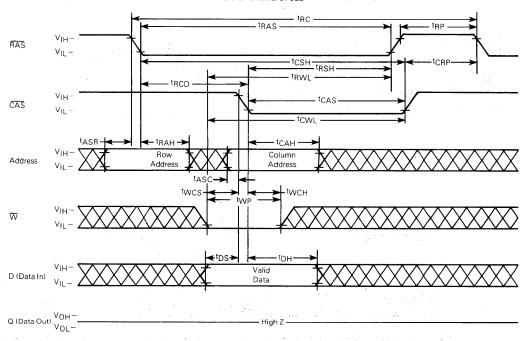

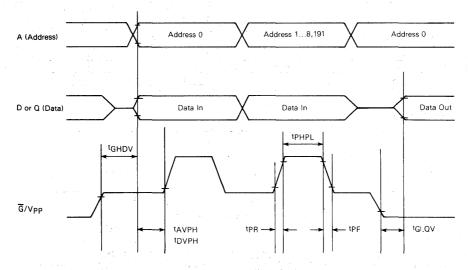

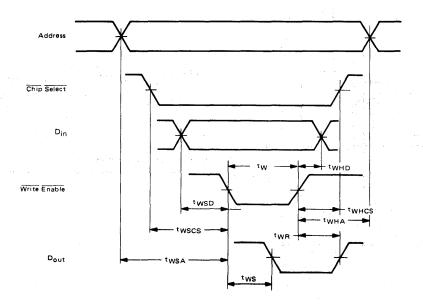

## WRITE CYCLE TIMING

## MCM4116B

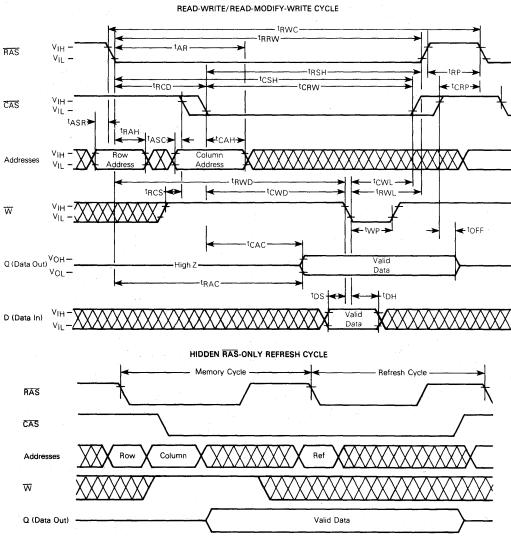

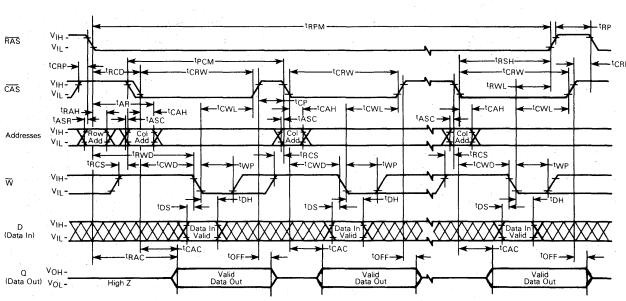

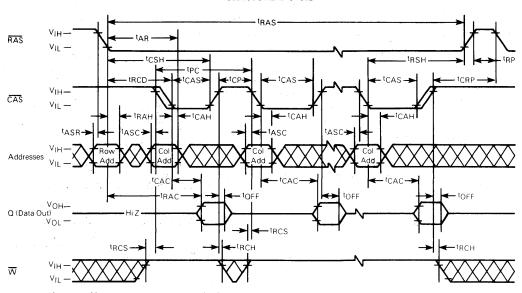

## READ-WRITE/READ-MODIFY-WRITE CYCLE

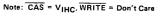

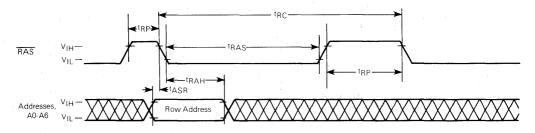

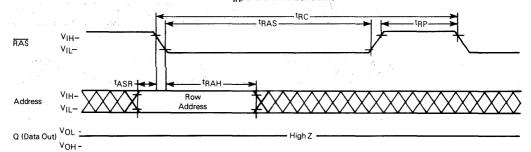

## RAS ONLY REFRESH TIMING

Vон-Dout VOL-

2-7

## MCM4116B

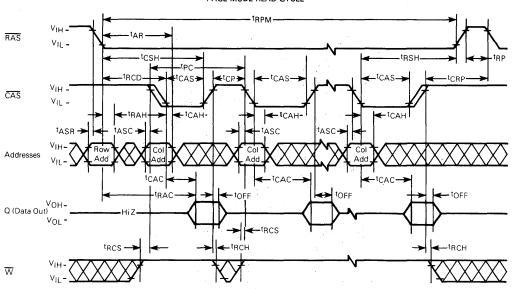

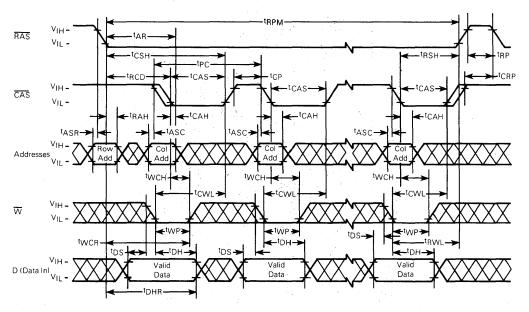

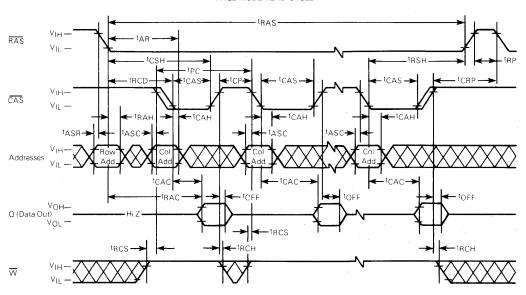

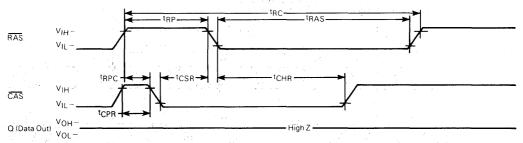

### PAGE MODE READ CYCLE

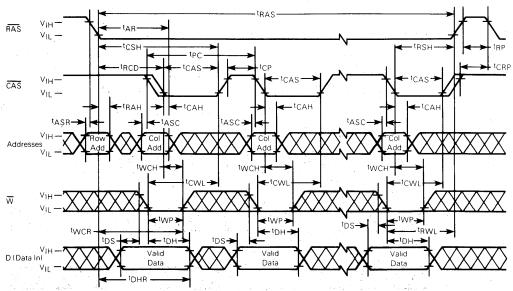

### PAGE MODE WRITE CYCLE

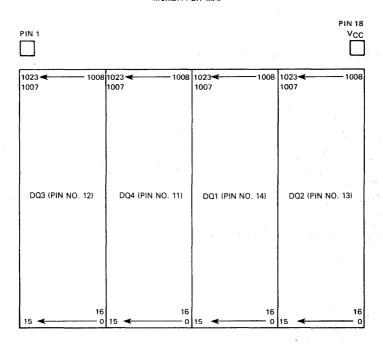

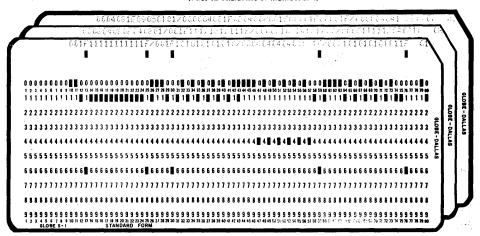

## MCM4116B BIT ADDRESS MAP

|              | Column Address A6                                                                       | A5 A4 A3 A2 A1 A0<br>A5 A4 A3 A2 A1 A0<br>Dws |                                         | Hex Dec<br>76 118<br>77 118                                                                                            |                                                                                                 |                                                                                                                     |

|--------------|-----------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|              | 0 = potential well filled<br>with electrons                                             | 1 = potential well filled<br>with electrons   |                                         | 16 22<br>17 23<br>14 20<br>15 21<br>12 18<br>13 19<br>10 16<br>11 17<br>1E 30<br>1F 31<br>1C 28<br>1D 29               | 0 0 1 0<br>0 0 1 1<br>0 0 1 1 | 1 1 0<br>1 1 1<br>1 0 0<br>1 0 1<br>0 1 0<br>0 1 1<br>0 0 0<br>0 0 1<br>1 1 0<br>1 1 0<br>1 1 1<br>1 0 0            |

|              | with electrons                                                                          |                                               |                                         | 1A 26<br>1B 27<br>18 24<br>19 25<br>OE 14<br>OF 15<br>OC 12<br>OD 13<br>OA 10<br>OB 11<br>OB 8<br>09 9<br>O6 6<br>O7 7 | 0 0 1 1 0 0 1 1 0 0 1 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1                                         | 0 1 0<br>0 1 1<br>0 0 0<br>0 0 1<br>1 1 0<br>1 1 1<br>1 0 0<br>1 0 1<br>0 1 0<br>0 1 1<br>0 0 0<br>0 0 1 1<br>1 1 0 |

|              | 0100 0000<br>0101 0001<br>0102 0003<br>0104 0004<br>0106 0005<br>0107 0007<br>0108 0008 |                                               | 017F 007F                               | 04 4<br>05 5<br>02 2<br>03 3<br>00 0                                                                                   | 0 0 0 0<br>0 0 0 0<br>0 0 0 0<br>0 0 0 0<br>0 0 0 0                                             | 1 0 0<br>1 0 1<br>0 1 0<br>0 1 1<br>0 0 0                                                                           |

| sassanny wou | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                   | 1 0 0 0 0 0 0 64 40                           | T 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 01 1                                                                                                                   |                                                                                                 | 0 0 1                                                                                                               |

## MCM4517

## 16,384-BIT DYNAMIC RAM

The MCM4517 is a 16,384-bit, high-speed, dynamic Random-Access Memory. Organized as 16,384 one-bit words and fabricated using HMOS high-performance, N-channel, silicon-gate technology. This new breed of 5-volt only dynamic RAM combines high performance with low cost and improved reliability.

By multiplexing row- and column-address inputs, the MCM4517 requires only seven address lines and permits packaging in standard 16-pin dual-in-line packages. Complete address decoding is done on chip with address latches incorporated. Data out is controlled by  $\overline{\text{CAS}}$  allowing for greater system flexibility.

All inputs and outputs, including clocks, are fully TTL compatible. The MCM4517 incorporates a one-transistor cell design and dynamic storage techniques.

- Organized as 16,384 Words of 1 Bit

- Single +5 Volt Operation

- Fast 100 ns Operation

- Low Power Dissipation:

170 mW Maximum (Active)

- 14 mW Maximum (Standby)

- Maximum Access Time

- MCM4517-10 100 ns

- MCM4517-12 120 ns

- MCM4517-15 150 ns

- MCM4517-20 200 ns ● Three-State Data Output

- Internal Latches for Address and Data input

- Early-Write Common I/O Output Capability

- 64K Compatible 128-cycle, 2 ms Refresh

- RAS-only Refresh Mode

- CAS Controlled Output

- Upward Pin Compatibility from the 16K RAM (MCM4116) to the 64K RAM (MCM6664)

- Allows Undershoot V<sub>II</sub> min = −2 V

- Hidden RAS Only Refresh Capability

## MOS

(N-CHANNEL, SILICON-GATE)

16,384-BIT DYNAMIC RAM

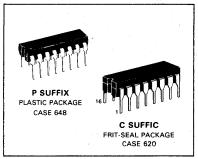

P SUFFIX

PLASTIC PACKAGE

CASE 648

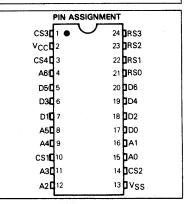

#### PIN ASSIGNMENT

| N/C               |     | 16 | þ | ۷ss |

|-------------------|-----|----|---|-----|

| D C               | 2   | 15 | þ | CAS |

| W                 | 3   | 14 | þ | Q   |

| RAS               | 4   | 13 | þ | A6  |

| A0 [              | 5   | 12 | þ | А3  |

| A2                | 6   | 11 | þ | A4  |

| A1 [              | 7 - | 10 | þ | A5  |

| v <sub>CC</sub> [ | 8   | 9  | þ | N/C |

| 1               | PIN NAMES             |  |  |  |  |  |  |  |  |  |

|-----------------|-----------------------|--|--|--|--|--|--|--|--|--|

| A0-A6           | Address Input         |  |  |  |  |  |  |  |  |  |

|                 | Data In               |  |  |  |  |  |  |  |  |  |

|                 | Data Out              |  |  |  |  |  |  |  |  |  |

|                 | Read/Write Input      |  |  |  |  |  |  |  |  |  |

|                 | Row Address Strobe    |  |  |  |  |  |  |  |  |  |

|                 | Column Address Strobe |  |  |  |  |  |  |  |  |  |

|                 | Power (+5 V)          |  |  |  |  |  |  |  |  |  |

| V <sub>SS</sub> | Ground                |  |  |  |  |  |  |  |  |  |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.

#### ABSOLUTE MAXIMUM RATINGS (See Note)

| Rating                             | Symbol                             | Value       | Unit |

|------------------------------------|------------------------------------|-------------|------|

| Voltage on Any Pin Relative to VSS | V <sub>in</sub> , V <sub>out</sub> | -2 to +7    | Vdc  |

| Operating Temperature Range        | TA                                 | 0 to +70    | °C   |

| Storage Temperature Range          | T <sub>stg</sub>                   | -65 to +150 | °C   |

| Power Dissipation                  | PD                                 | 1.0         | W    |

| Data Out Current                   | lout                               | 50          | mA   |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

#### DC OPERATING CONDITIONS AND CHARACTERISTICS

(Full Operating Voltage and Temperature Range Unless Otherwise Noted.)

## RECOMMENDED DC OPERATING CONDITIONS

| Parameter                   | Symbol | Min  | Тур | Max                | Unit | Notes |

|-----------------------------|--------|------|-----|--------------------|------|-------|

| Supply Voltage              | Vcc.   | 4.5  | 5.0 | 5.5                | V    | 1     |

| Supply Voltage              | Vss    | 0    | 0   | 0                  | Ľ    |       |

| Logic 1 Voltage, All Inputs | VIH    | 2.4  | -   | V <sub>CC</sub> +1 | ٧    | 1     |

| Logic 0 Voltage, All Inputs | VIL    | -2.0 | -   | 0.8                | V    | 1     |

## DC CHARACTERISTICS

| Characteristics                                                       | Symbol | Min | Тур  | Max | Units | Notes |

|-----------------------------------------------------------------------|--------|-----|------|-----|-------|-------|

| VCC Supply Current (Standby)                                          | ICC1   | _   | 1.8  | 2.5 | mA    | 5     |

| VCC Supply Current (Operating)                                        |        |     |      |     |       |       |

| 4517-10, t <sub>RC</sub> = 235                                        | lana   | l – | 22   | 31  | mA    | 4     |

| 4517-12, t <sub>RC</sub> = 270                                        | CC2    | -   | 20 . | 28  | "IA   | 4     |

| 4517-15, t <sub>RC</sub> = 320                                        | 1      | _   | - 18 | 25  |       |       |

| 4517-20, t <sub>RC</sub> =350                                         | 1      | -   | 16   | 23  |       | i     |

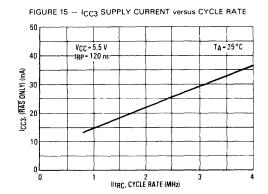

| V <sub>CC</sub> Supply Current (RAS-Only Cycle)                       |        |     |      |     |       |       |

| $4517-10$ , $t_{RC} = 235$                                            | lana   | -   | 14   | 23  | mA    | 4     |

| 4517-12, t <sub>RC</sub> = 270                                        | 1CC3   | l – | 12   | 21  | IIIA  | , 4   |

| 4517-15, t <sub>RC</sub> = 320                                        | -      |     | - 11 | 19  |       | ĺ     |

| 4517-20, t <sub>RC</sub> =350                                         | _1     |     | 10   | 18  |       |       |

| VCC Standby Current (Standby, Output Enable) (CAS at VIL, RAS at VIH) | ICC4   |     | 2    | 5   | mA    |       |

| VCC Supply Current (Page Mode Cycle Only)                             |        |     |      |     |       | 1     |

| 4517-10, t <sub>RC</sub> = 235                                        |        | -   | 17   | 23  | -     |       |

| 4517-12, t <sub>RC</sub> =270                                         | ICC5   | -   | 15   | 21  | mA    | l     |

| 4517-15, t <sub>RC</sub> = 320                                        |        | -   | 13   | 18  |       | l     |

| 4517-20, t <sub>RC</sub> =350                                         |        | -   | 10   | 15  |       | l     |

| Input Leakage Current (Any Input) (VSS≤Vin≤VCC)                       | li(L)  | _   | _    | 10  | μΑ    |       |

| Output Leakage Current (0≤V <sub>out</sub> ≤5.5) (CAS at Logic 1)     | IO(L)  | _   | _    | 10  | μΑ    |       |

| Output Logic 1 Voltage@lout = -4 mA                                   | VOH    | 2.4 | _    | _   | V     |       |

| Output Logic 0 Voltage@I <sub>out</sub> =4 mA                         | VOL    | _   | _    | 0.4 | V     |       |

### AC OPERATING CONDITIONS AND CHARACTERISTICS

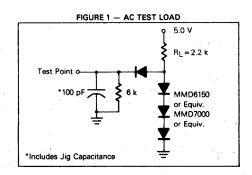

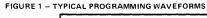

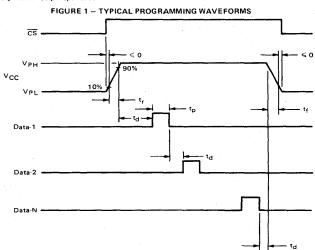

(Full Operating Voltage and Temperature Range Unless Otherwise Noted) (See Notes 2, 3, 9, 14 and Figure 1)

| Parameter                                  | Symbol MCM4517-10 MCM4517-12 MCM4517-15 MCM4517-2 |     |       |      |       |     |       |     | 4517-20 | Unit | Notes  |

|--------------------------------------------|---------------------------------------------------|-----|-------|------|-------|-----|-------|-----|---------|------|--------|

| Parameter                                  | Symbol                                            | Min | Max   | Min  | Max   | Min | Max   | Min | Max     | Onit | NOTES  |

| Random Read or Write Cycle Time            | tRC                                               | 235 | -     | 270  | -     | 320 | _     | 360 | -       | ns   | 8, 9   |

| Read-Modify-Write Cycle Time               | tRWC                                              | 285 | -     | 320  | _     | 410 |       | 440 | -       | ns   | 8, 9   |

| Access Time from Row Address Strobe        | tRAC                                              | -   | 100   | _    | 120   | -   | 150   | -   | 200     | ns   | 10, 12 |

| Access Time from Column Address Strobe     | tCAC                                              | -   | 55    |      | 65    | _   | 80    |     | 120     | ns   | 11, 12 |

| Output Buffer and Turn-Off Delay           | tOFF                                              | 0   | 45    | 0    | 50    | 0   | 60    | 0   | 70      | ns   | 18     |

| Row Address Strobe Precharge Time          | tRP                                               | 110 | -     | 120  |       | 135 |       | 150 | -       | ns   |        |

| Row Address Strobe Pulse Width             | tRAS                                              | 115 | 10000 | 140  | 10000 | 175 | 10000 | 200 | 10000   | ns   | 19     |

| Column Address Strobe Pulse Width          | tCAS                                              | 55  | 10000 | 65   | 10000 | 95  | 10000 | 120 | 10000   | ns   | 19     |

| Row to Column Strobe Lead Time             | tRCD                                              | 25  | 45    | 25   | 55    | 25  | 70    | 30  | 80      | ns   | 13     |

| Row Address Setup Time                     | tASR                                              | 0   | - '   | .0   | _     | 0   | -     | 0   | -       | ns   |        |

| Row Address Hold Time                      | tRAH                                              | 15  | -     | 15   | _     | 20  | _     | 25  | _       | ns   |        |

| Column Address Setup Time                  | tASC                                              | 0   | -     | 0    | -     | 0   | _     | 0   | -       | ns   |        |

| Column Address Hold Time                   | tCAH                                              | 15  | -     | 15   | -     | 20  | -     | 20  | -       | ns   |        |

| Column Address Hold Time Referenced to RAS | tAR                                               | 60  |       | . 70 | -     | 90  | _     | 140 | _       | ns   |        |

| Transition Time (Rise and Fall)            | tΤ                                                | 3   | 50    | 3    | 50    | 3   | 50    | 3   | 50      | ns   | 6      |

### AC OPERATING CONDITIONS AND CHARACTERISTICS (Continued)

| Parameter                                 | Symbol           | MCM4 | 517-10 | MCM4 | 517-12 | MCM4 | 1517-15 | MCM4 | 517-20 | Unit | Notes  |

|-------------------------------------------|------------------|------|--------|------|--------|------|---------|------|--------|------|--------|

| Parameter                                 | Symbol           | Min  | Max    | Min  | Max    | Min  | Max     | Min  | Max    | Onne | 140105 |

| Read Command Setup Time                   | TRCS             | 0    | - 1    | 0    | - 1    | 0    |         | 0    |        | ns   |        |

| Read Command Hold Time                    | tRCH             | 0    | 1-     | 0    | -      | 0    | _       | 0    | -      | ns   | 14     |

| Read Command Hold Time Referenced to RAS  | tRRH             | 20   | _      | 25   | _      | 35   | _       | 40   |        | ns   | 14     |

| Write Command Hold Time                   | tWCH             | 25   | _      | 30   | -      | 45   | _       | 60   |        | ns.  |        |

| Write Command Hold Time Referenced to RAS | tWCR             | 70   | _      | 85   | -      | 115  |         | 140  |        | ns   |        |

| Write Command Pulse Width                 | tWP              | 25   | -      | 30   | -      | 50   |         | 50   | _      | ns   |        |

| Write Command to Row Strobe Lead Time     | tRWL             | 60   | _      | 65   | -      | 110  | -       | 110  | -      | ns   |        |

| Write Command to Column Strobe Lead Time  | tCWL             | 45   | _      | 50   | - '    | 100  | -       | 100  | _      | ns   |        |

| Data in Setup Time                        | tDS              | 0    | _      | 0    | -      | 0    | _       | 0    | _      | ns   | 15     |

| Data in Hold Time                         | t <sub>DH</sub>  | 25   | _      | 30   | -      | 45   | -       | 60   |        | ns   | 15     |

| Data in Hold Time Referenced to RAS       | tDHR             | 70   |        | 85   | -      | 115  | -       | 140  |        | ns   |        |

| Column to Row Strobe Precharge Time       | tCRP             | 0    |        | 0    | _      | 0    | -       | 0    | . —    | ns   |        |

| RAS Hold Time                             | tRSH             | 70   | -      | 85   |        | 105  |         | 120  | -      | ns   |        |

| Refresh Period                            | tRFSH            | _    | 2.0    | _    | 2.0    |      | 2.0     | -    | 2.0    | ms   |        |

| Write Command Setup Time                  | twcs             | 0    | -      | 0    |        | 0    |         | 0    |        | ns   | 16     |

| CAS to WRITE Delay                        | tCWD             | 55   | 1      | 65   |        | 80   | -       | 100  | -      | ns   | 16     |

| RAS to WRITE Delay                        | tRWD             | 100  | _      | 120  |        | 150  |         | 160  |        | ns   | 16     |

| CAS Hold Time                             | tCSH             | 100  | _      | 120  |        | 165  |         | 200  | -      | ns   |        |

| CAS Precharge, Non Page Mode              | tCPN             | 50   | -      | 55   | _      | 70   | _       | 90   | _      | ns   |        |

| RMW Cycle RAS Pulse Width                 | tRRW             | 135  | 10000  | 160  | 10000  | 195  | 10000   | 220  | 10000  | ns   |        |

| RMW Cycle CAS Pulse Width                 | tCRW             | 95   | 10000  | 110  | 10000  | 130  | 10000   | 140  | 10000  | ns   |        |

| Page Mode Cycle Time                      | tPC_             | 125  | -      | 145  | _      | 190  | _       | 260  | _      | ns   |        |

| Page Mode Cycle Time (Read-Modify-Write)  | <sup>t</sup> PCM | 175  | -      | 200  | _      | 280  |         | 360  | -      | ns   |        |

| CAS Precharge Time (Page Mode Cycle Only) | tCP              | 60   | _      | 70   |        | 85   | _       | 105  |        | ns   |        |

| RAS Pulse Width (Page Mode Cycle Only)    | tRPM             | 115  | 10000  | 140  | 10000  | 175  | 10000   | 235  | 10000  | ns   |        |

### **CAPACITANCE** (f = 1.0 MHz, $T_A = 25$ °C, $V_{CC} = +5$ V. Periodically sampled rather than 100% tested.)

| Parameter                         | Symbol          | Тур | Max | Units | Notes |

|-----------------------------------|-----------------|-----|-----|-------|-------|

| Input Capacitance (A0-A6), Din    | C <sub>11</sub> | 4.0 | 5.0 | рF    | 7     |

| Input Capacitance RAS, CAS, WRITE | C <sub>12</sub> | 5.0 | 7.0 | рF    | 7     |

#### NOTES.

- All voltages referenced to V<sub>SS</sub>.

- 2. VIH min and VIL max are reference levels for measuring timing of input signals. Transition times are measured between VIH and VIL.

- 3. An initial pause of 100 µs is required after power-up followed by any 8 RAS cycles before proper device operation guaranteed.

- 4. Current is a function of cycle rate and output loading; maximum current is measured at the fastest cycle rate with the output open.

- Output is disabled (open-circuit) and RAS and CAS are both at a logic 1.

- 6. The transition time specification applies for all input signals. In addition to meeting the transition rate specification, all input signals must transmit between VIH and VIL (or between VIL and VIH) in a monotonic manner.

- 7. Capacitance measured with a Boonton Meter or effective capacitance calculated from the equation:  $C = I_{\Delta t}/\Delta V$

- 8. The specifications for tac (min), and tawe (min) are used only to indicate cycle time at which proper operation over the full temperature range (0°C $\leq$ T $_{A}\leq$ 70°C) is assured.

- 9. AC measurements assume  $t_T = 5.0$  ns. 10. Assumes that tRCD≤tRCD (Max)

- 11. Assumes that tRCD≥tRCD (Max)

- 12. Measured with a current load equivalent to 2 TTL loads (+200  $\mu$ A, -4 mA) and 100 pF (V<sub>OH</sub>=2.0 V, V<sub>OL</sub>=0.8 V).

- 13. Operation within the tRCD (max) limit ensures that tRAC (max) can be met, tRCD (max) is specified as a reference point only; if tRCD is greater than the specified tRCD (max) limit, then access time is controlled exclusively by tCAC.

- 14. Either tara track that is satisfied for a read cycle.

15. These parameters are referenced to CAS leading edge in random write cycles and to WRITE leading edge in delayed write or readmodify-write cycles.

- 16. tWCS, tCWD, and tRWD are not restrictive operating parameters. They are included in the data sheet as electrical characteriistics only: if twcs twcs (min), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout the entire cycle; if tcwp tcwp (min) and tqwp tcwp (min), the cycle is a read-write cycle and the data out will contain data read from the selected cell; if neither of the above sets of conditions is satisfied, the condition of the data out (at access time) is indeterminate

- 17. Addresses, data-in and WRITE are don't care. Data-out depends on the state of CAS. If CAS remains low, the previous output will remain valid. CAS is allowed to make an active to inactive transition during the RAS-only refresh cycle. When CAS is brought high, the output will assume a high-impedance state.

- 18. toff (max) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

- 19. For read and write cycles only.

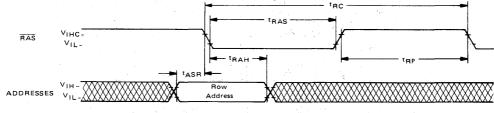

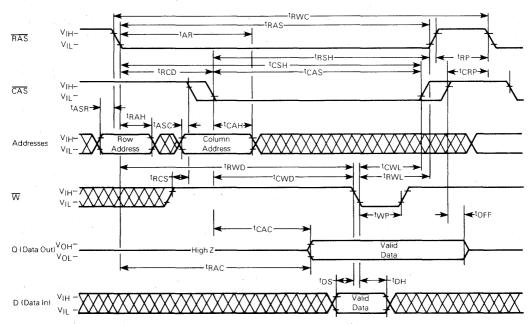

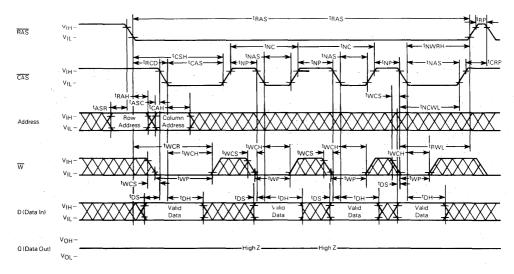

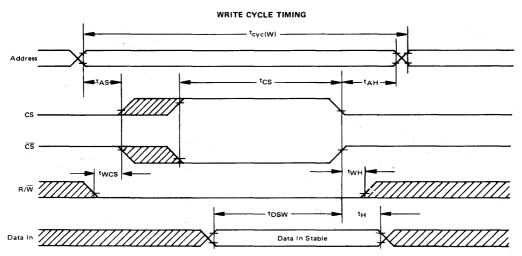

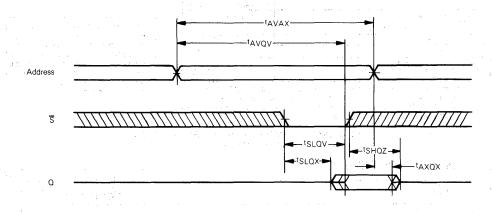

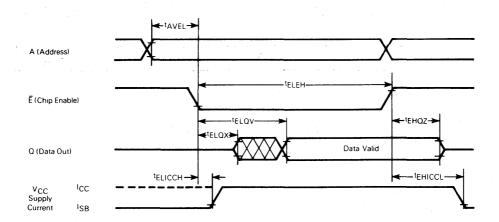

### READ CYCLE TIMING

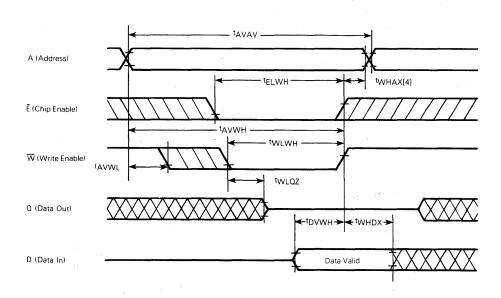

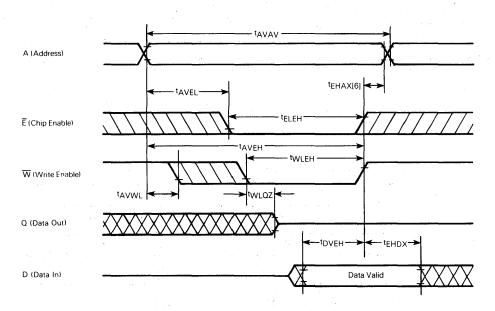

### WRITE CYCLE TIMING

RAS VIHVIL

Addresses, AO-A6

VIL

READ-WRITE/READ-MODIFY-WRITE CYCLE

(Data-In and Write are Don't Care, CAS is HIGH)

\*\*RAS\*\*

\*\*IRAH\*\*

READ-WRITE/READ-MODIFY-WRITE CYCLE

### PAGE MODE WRITE CYCLE

## MCM6665A

#### 64K BIT DYNAMIC RAM

The MCM6665A is a 65,536 bit, high-speed, dynamic Random-Access Memory. Organized as 65,536 one-bit words and fabricated using HMOS high-performance N-channel silicon-gate technology, this new breed of 5-volt only dynamic RAM combines high performance with low cost and improved reliability.

By multiplexing row- and column-address inputs, the MCM6665A requires only eight address lines and permits packaging in standard 16-pin dual-in-line packages. Complete address decoding is done on chip with address latches incorporated. Data out is controlled by CAS allowing for greater system flexibility.

All inputs and outputs, including clocks, are fully TTL compatible. The MCM6665A incorporates a one-transistor cell design and dynamic storage techniques

- Organized as 65,536 Words of 1 Bit

- Single +5 V Operation (± 10%)

- · Full Power Supply Range Capabilities

- Maximum Access Time

MCM6665A-15 = 150 ns

- MCM6665A-20 = 200 ns

- Low Power Dissipation 302.5 mW Maximum (Active) (MCM6665A-15) 22 mW Maximum (Standby)

- Three-State Data Output

- Internal Latches for Address and Data Input

- Early-Write Common I/O Capability

- 16K Compatible 128-Cycle, 2 ms Refresh

- RAS-only Refresh Mode

- CAS Controlled Output

- Upward Pin Compatible from the 16K RAM (MCM4116, MCM4517)

- Fast Page Mode Cycle Time

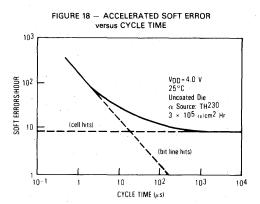

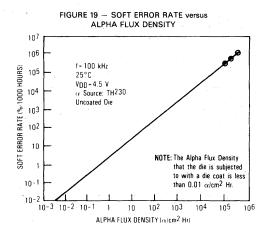

- Low Soft Error Rate < 0.1% per 1000 Hours (See Soft Error Testing)</li>

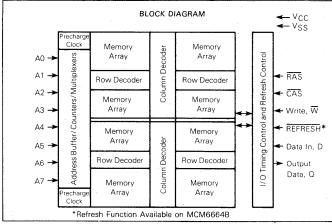

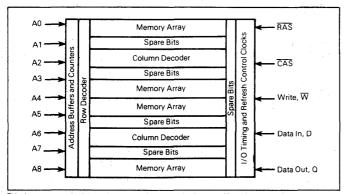

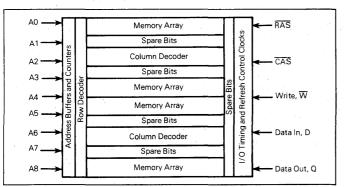

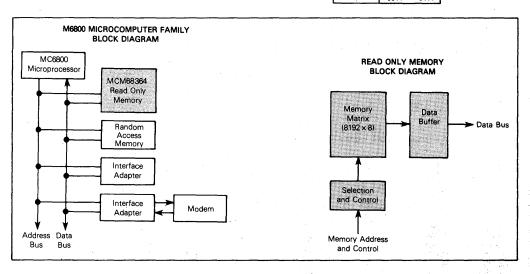

#### **BLOCK DIAGRAM** - Vcc **←** V<sub>SS</sub> Clock Memory Memory Decoder Array Array and Refresh Control Buffer/Counters/Multiplexers A0 -**←** RAS A1 -Row Decoder Column Row Decoder A2 ← ĈAS Memory Memory A3 → Array Array ← Write, W̄ Control A4 → ◆ REFRESH\* Memory Memory Array Array Decoder A5 -← Data In, D I/O Timing Row Decoder Row Decoder Address A6 -Output Column Data, Q A7 -Memory Memory recharg Array Array Clock \*Refresh Function Available on MCM6664A

## MOS

(N-CHANNEL, SILICON-GATE)

65,536-BIT DYNAMIC RANDOM ACCESS **MEMORY**

P SUFFIX PLASTIC PACKAGE **CASE 648**

### PIN ASSIGNMENT

| N/C.            |     | 16 | b vs        |

|-----------------|-----|----|-------------|

| D <b>C</b>      | 2   | 15 | CA:         |

| w c             | 3 - | 14 | a           |

| RAS             | 4   | 13 | A6          |

| A0 <b>[</b>     | 5   | 12 | <b>1</b> A3 |

| A2 <b>C</b>     | 6   | 11 | A4          |

| . A1            | 7   | 10 | <b>A</b> 5  |

| V <sub>CC</sub> | 8   | 9  | A7          |

| PIN NAMES                   |    |  |  |  |  |  |  |  |

|-----------------------------|----|--|--|--|--|--|--|--|

| A0-A7 Address Inpu          | ıŧ |  |  |  |  |  |  |  |

| D                           | n  |  |  |  |  |  |  |  |

| Q Data Ou                   | Jt |  |  |  |  |  |  |  |

| W Read/Write Inpu           | υt |  |  |  |  |  |  |  |

| RAS Row Address Strob       | е  |  |  |  |  |  |  |  |

| CAS Column Address Strob    | е  |  |  |  |  |  |  |  |

| V <sub>CC</sub> Power (+5 \ | /) |  |  |  |  |  |  |  |

| V <sub>SS</sub> Groun       | d  |  |  |  |  |  |  |  |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this highimpedance circuit.

#### ABSOLUTE MAXIMUM RATINGS (See Note)

| Rating                                                        | Symbol                             | Value       | Unit |  |

|---------------------------------------------------------------|------------------------------------|-------------|------|--|

| Voltage on Any Pin Relative to VSS (except VCC)               | V <sub>in</sub> , V <sub>out</sub> | -2 to +7    | V    |  |

| Voltage on V <sub>CC</sub> Supply Relative to V <sub>SS</sub> |                                    |             |      |  |

| Operating Temperature Range                                   | TA                                 | 0 to +70    | °C   |  |

| Storage Temperature Range                                     | T <sub>stg</sub>                   | -65 to +150 | °C   |  |

| Power Dissipation                                             | PD                                 | 1.0         | W    |  |

| Data Out Current                                              | lout                               | 50          | mΑ   |  |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

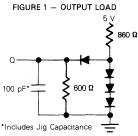

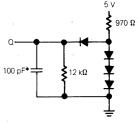

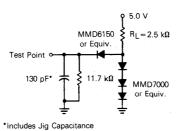

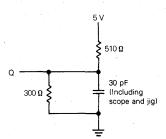

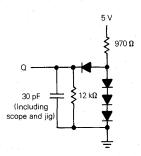

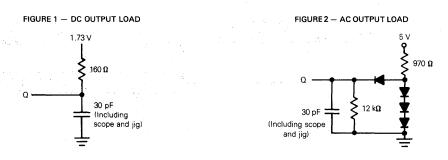

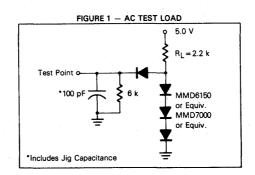

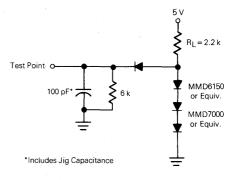

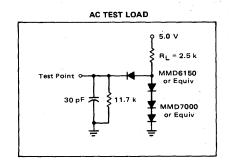

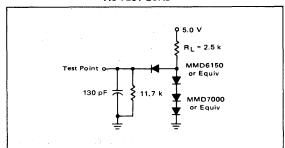

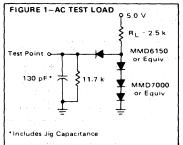

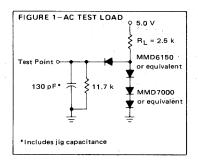

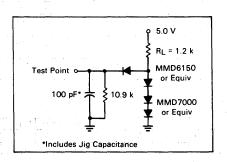

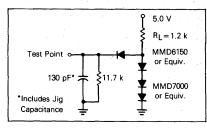

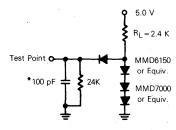

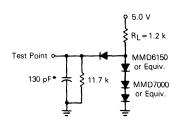

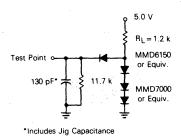

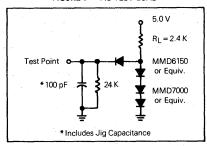

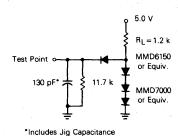

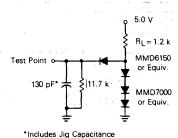

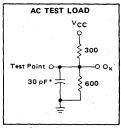

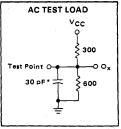

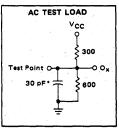

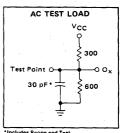

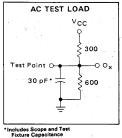

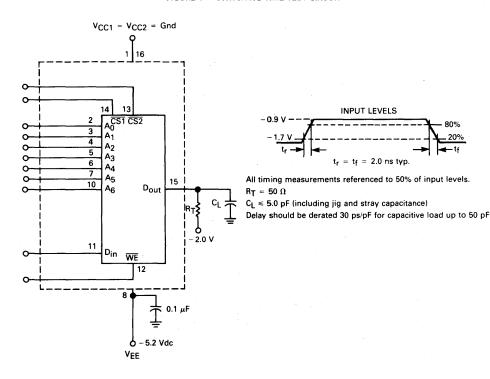

# 5 V \$970 Ω 100 pF\* 12 kΩ Ψ

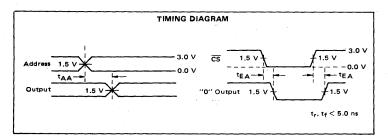

FIGURE 1 - OUTPUT LOAD

\*Includes Jig Capacitance

#### DC OPERATING CONDITIONS AND CHARACTERISTICS

(Full operating voltage and temperature range unless otherwise noted.)

#### RECOMMENDED OPERATING CONDITIONS

| Parameter                   | Symbol          | Min    | Тур | Max                 | Unit | Notes |

|-----------------------------|-----------------|--------|-----|---------------------|------|-------|

| Supply Voltage              | Vcc             | 4.5    | 5.0 | 5.5                 | ٧    | 1     |

|                             | VSS             | 0      | 0   | 0                   | ٧    | 1     |

| Logic 1 Voltage, All Inputs | VIH             | 2.4    | -   | V <sub>CC</sub> + 1 | ٧    | 1 .   |

| Logic 0 Voltage, All Inputs | V <sub>IL</sub> | - 1.0° | _   | 0.8                 | V    | 1     |

<sup>\*</sup>The device will withstand undershoots to the -2 volt level with a maximum pulse width of 20 ns at the -1.5 volt level. This is periodically sampled rather than 100% tested.

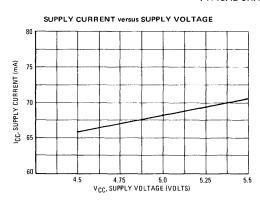

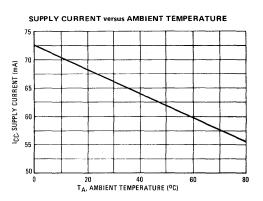

### DC CHARACTERISTICS

| Characteristic                                                                                                                                                   | Symbol           | Min | Max      | Units | Notes |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|----------|-------|-------|

| V <sub>CC</sub> Power Supply Current (Standby)                                                                                                                   | lcc2             |     | 4.0      | mA    | 5_    |

| V <sub>CC</sub> Power Supply Current<br>6665A-15, t <sub>RC</sub> ≈ 270 ns<br>6665A-20, t <sub>RC</sub> = 330 ns                                                 | lcc1             | 1.1 | 55<br>50 | mA    | 4     |

| V <sub>CC</sub> Power Supply Current During RAS only Refresh Cycles 6665A-15, t <sub>RC</sub> = 270 ns 6665A-20, t <sub>RC</sub> = 330 ns                        | ICC3             |     | 45<br>40 | mA    | 4     |

| V <sub>CC</sub> Power Supply Current During Page Mode Cycle for $t_{RAS} = 10 \mu sec$ 6665A-15, $t_{PC} = t_{RP} = 145 ns$ 6665A-20, $t_{PC} = t_{RP} = 200 ns$ | <sup>1</sup> CC4 |     | 40<br>35 | mA    | 4     |

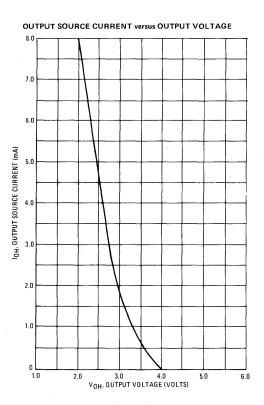

| Input Leakage Current (VSS≤V <sub>in</sub> ≤VCC)                                                                                                                 | l(L)             |     | 10       | μΑ    | -     |

| Output Leakage Current (CAS at logic 1, VSS≤Vout≤VCC)                                                                                                            | lO(L)            | -   | 10       | μΑ    | -     |

| Output Logic 1 Voltage @ I <sub>out</sub> = -4 mA                                                                                                                | Voн              | 2.4 | -        | V     |       |

| Output Logic 0 Voltage @ I <sub>out</sub> = 4 mA                                                                                                                 | VOL              |     | 0.4      | ٧     | _     |

### **CAPACITANCE** (f = 1.0 MHz, $T_A = 25$ °C, $V_{CC} = 5$ V Periodically Sampled Rather Than 100% Tested)

| Parameter                                             | Symbol          | Тур | Max | Unit | Notes |

|-------------------------------------------------------|-----------------|-----|-----|------|-------|

| Input Capacitance (A0-A7), D                          | C <sub>l1</sub> | 3   | 5   | pF   | . 7   |

| Input Capacitance RAS, CAS, WRITE                     | C <sub>I2</sub> | 6   | 8   | pF   | 7     |

| Output Capacitance (Q), (CAS = VIH to disable output) | CO              | 5   | 7   | pF   | 7     |

- NOTES: 1. All voltages referenced to VSS.

- 2. V<sub>IH</sub> min and V<sub>IL</sub> max are reference levels for measuring timing of input signals. Transition times are measured between V<sub>IH</sub> and V<sub>IL</sub>.

- 3. An initial pause of 100 µs is required after power-up followed by any 8 RAS cycles before proper device operation is guaranteed

- Current is a function of cycle rate and output loading; maximum current is measured at the fastest cycle rate with the output open.

- 5. RAS and CAS are both at a logic 1.

- 6. The transition time specification applies for all input signals. In addition to meeting the transition rate specification, all input signals must transit between V<sub>IH</sub> and V<sub>IL</sub> (or between V<sub>IL</sub> and V<sub>IH</sub>) in a monotonic manner.

- 7. Capacitance measured with a Boonton Meter or effective capacitance calculated from the equation:  $C = \frac{i\Delta t}{\Delta V}$

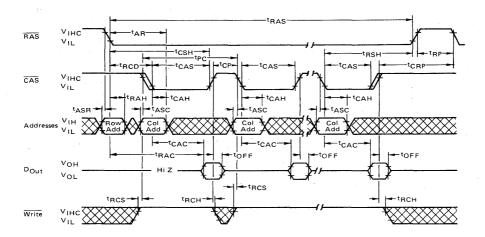

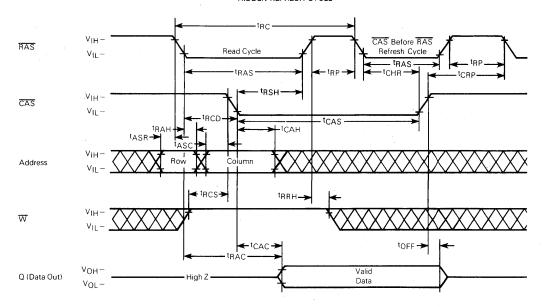

## MCM6665A

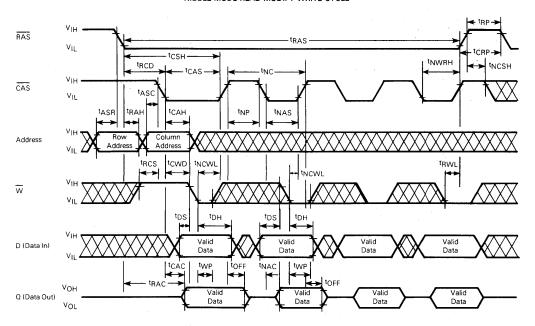

## AC OPERATING CONDITIONS AND CHARACTERISTICS (Read, Write, and Read-Modify-Write Cycles) (Full Operating Voltage and Temperature Range Unless Otherwise Noted; See Notes 2, 3, 6, and Figure 1)

| Parameter                                  |                  | 6665A-15 |       | 6665A-20    |       |       |        |

|--------------------------------------------|------------------|----------|-------|-------------|-------|-------|--------|

|                                            | Symbol           | Min      | Max   | Min         | Max   | Units | Notes  |

| Random Read or Write Cycle Time            | tRC              | 270      | -     | 330         |       | ns    | 8, 9   |

| Read Write Cycle Time                      | tRWC             | 280      | -     | 330         | _     | ns    | 8, 9   |

| Access Time from Row Address Strobe        | tRAC             | _        | 150   | -           | 200   | ns    | 10, 12 |

| Access Time from Column Address Strobe     | tCAC             | _        | 75    |             | 100   | ns    | 11, 12 |

| Output Buffer and Turn-Off Delay           | tOFF             | 0        | 30    | 0           | 40    | ns    | 18     |

| Row Address Strobe Precharge Time          | tRP              | 100      | -     | 120         | _     | ns    | _      |

| Row Address Strobe Pulse Width             | tRAS             | 150      | 10000 | 200         | 10000 | ns    | _      |

| Column Address Strobe Pulse Width          | tCAS             | 75       | 10000 | 100         | 10000 | ns    | _      |

| Row to Column Strobe Lead Time             | tRCD             | 30       | 75    | 30          | 100   | ns    | 13     |

| Row Address Setup Time                     | tASR             | 0        | -     | 0           | _     | ns    | -      |

| Row Address Hold Time                      | tRAH             | 20       | -     | 25          | _     | ns    |        |

| Column Address Setup Time                  | · tASC           | 0        | -     | 0           |       | ns    | -      |

| Column Address Hold Time                   | t <sub>CAH</sub> | 35       | -     | 45          |       | ns    | -      |

| Column Address Hold Time Referenced to RAS | tAR              | 95       | -     | 120         | -     | ns    | 17     |

| Transition Time (Rise and Fall)            | t <sub>T</sub>   | 3        | 50    | 3           | 50    | ns    | 6      |

| Read Command Setup Time                    | tRCS             | 0        | -     | 0           | _     | ns    |        |

| Read Command Hold Time                     | <sup>t</sup> RCH | 0        | -     | 0           | _     | ns    | 14     |

| Read Command Hold Time Referenced to RAS   | trrh             | 0        | _     | 0           | _     | ns    | 14     |

| Write Command Hold Time                    | tWCH             | 35       | _     | 45          | -     | ns    | _      |

| Write Command Hold Time Referenced to RAS  | tWCR             | 95       | _     | 120         | -     | ns    | 17     |